Fターム[5F110NN03]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935) | 複数層 (3,316)

Fターム[5F110NN03]に分類される特許

321 - 340 / 3,316

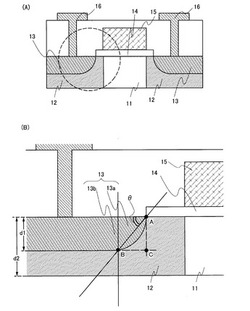

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

酸化物半導体層

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

部材の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生

産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向か

って結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化

物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部

材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の

同軸(アキシャル)成長をさせていることである。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、下層側の第1導電体部および上層側の第2導電体部と、第1の導電体部と第2の導電体部との間に設けられた、厚膜状の絶縁体層と、この絶縁体層に対する貫通孔の内面形状に倣うように形成され、第1導電体部と第2導電体部とを電気的に接続するコンタクト部とを備え、貫通孔のテーパ角が鋭角となっている。

(もっと読む)

アクティブマトリクス基板及びそれを備えた表示パネル

【課題】フォトマスクの枚数を増やすことなく、酸化物半導体の半導体層を用いたTFTの特性の低下を抑制することにある。

【解決手段】マトリクス状の複数の画素電極Pと、各画素電極Pに接続されたTFT5と、互いに平行に延びる複数のソース線15aとを備え、TFT5が、絶縁基板10上のゲート電極11aと、ゲート電極11aを覆うゲート絶縁膜12aと、ゲート絶縁膜12a上でゲート電極11aに重なる酸化物半導体層13aと、酸化物半導体層13aに接続されたソース電極17a及びドレイン電極17bとを備え、ソース電極17a及びドレイン電極17bと酸化物半導体層13aとの間には、酸化物半導体層13aを覆う保護絶縁膜14aが設けられ、各ソース線15aは、金属材料により形成され、ソース電極17a及びドレイン電極17bは、各画素電極Pと同一材料により形成されている。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理を行った酸化物半導体膜を含み、且つ、作製工程において酸素ドープ処理されたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置をより少ない工程で作製する。

【解決手段】トランジスタと、画素電極とを有し、トランジスタは、第1のゲート電極と、第1のゲート電極上の第1の絶縁層と、第1の絶縁層上の半導体層と、半導体層上の第2の絶縁層と、第2の絶縁層上の第2のゲート電極とを有し、第1のゲート電極は、第1の絶縁層を介して、半導体層と重なる領域を有し、第2のゲート電極は、第2の絶縁層を介して、半導体層と重なる領域を有し、画素電極は、第2の絶縁層上に設けられ、第1の領域は、第2のゲート電極の少なくとも一部が、半導体層の少なくとも一部と重なる領域のうちの、少なくとも一部の領域であり、第2の領域は、画素電極が設けられた領域のうちの、少なくとも一部の領域であり、第1の領域における第2の絶縁層は、第2の領域における第2の絶縁層よりも薄い。

(もっと読む)

半導体装置

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを

目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かっ

て成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2

の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層

と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と

、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、

第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置であ

る。

(もっと読む)

デバイスおよび表示装置

【課題】基板上に形成された絶縁膜の応力を低減し、歩留まりが向上したデバイスおよびこのデバイスを備えた表示装置を提供する。

【解決手段】本開示の表示装置は、基板と、基板上の一部の領域に形成された金属層と、金属層上に設けられると共に、金属層未形成領域の少なくとも一部に溝を有する第1絶縁膜とを備える。

(もっと読む)

薄膜トランジスタ

【課題】高移動度の薄膜トランジスタ、その製造方法及びその製造に用いるスパッタリングターゲットを提供する。

【解決手段】元素In,Ga及びZnを下記領域1、2又は3の原子比の範囲で含む酸化物を活性層とし、電界効果移動度が25cm2/Vs以上である薄膜トランジスタ。

領域1

0.58≦In/(In+Ga+Zn)≦0.68

0.15<Ga/(In+Ga+Zn)≦0.29

領域2

0.45≦In/(In+Ga+Zn)<0.58

0.09≦Ga/(In+Ga+Zn)<0.20

領域3

0.45≦In/(In+Ga+Zn)<0.58

0.20≦Ga/(In+Ga+Zn)≦0.27

(もっと読む)

321 - 340 / 3,316

[ Back to top ]