Fターム[5F110NN33]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 製法 (8,383) | 堆積 (7,357)

Fターム[5F110NN33]の下位に属するFターム

Fターム[5F110NN33]に分類される特許

121 - 140 / 1,509

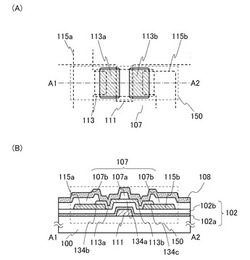

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜上に金属元素を含む絶縁膜を形成し、注入法により該金属元素を含む絶縁膜を通過して導入されたドーパントを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸化物半導体を用いた薄膜トランジスタにおいては、酸素原子等を酸化物半導体中に十分かつ均一に拡散させることが困難である。

【解決手段】半導体装置であって、ゲート電極と、前記ゲート電極の一方の表面を覆うように配置されたゲート絶縁膜と、前記ゲート絶縁膜に重ねて配置された酸化物半導体と、前記酸化物半導体に重ねて配置されたソース電極及びドレイン電極と、前記ソース電極及びドレイン電極と、前記ゲート絶縁膜層との間に、前記酸化物半導体に接するように配置された酸素原子含有膜と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

光及び熱エネルギー架橋性有機薄膜トランジスタ絶縁層材料

【課題】閾値電圧の絶対値及びヒステリシスが小さい有機薄膜トランジスタを製造しうる有機薄膜トランジスタ絶縁層材料を提供すること。

【解決手段】(A)分子内にビニルオキシ基を含有する低分子化合物及び/又は分子内にビニルオキシ基及び活性水素と反応しうる第2の官能基を電磁波の照射もしくは熱の作用により生成しうる第1の官能基を含有する高分子化合物と、(B)分子内にN−マレオイルアミノ基を含含有する低分子化合物及び/又は分子内にN−マレオイルアミノ基及び活性水素と反応しうる第2の官能基を電磁波の照射もしくは熱の作用により生成しうる第1の官能基を含有する高分子化合物とを、含有し、前記2種類の高分子化合物のうちの少なくとも一方の高分子化合物を含有する有機薄膜トランジスタ絶縁層材料。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

121 - 140 / 1,509

[ Back to top ]