Fターム[5F110NN41]の内容

Fターム[5F110NN41]の下位に属するFターム

Fターム[5F110NN41]に分類される特許

21 - 40 / 43

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性を向上させる。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、第13族元素および酸素を含む材料を用いて酸化物半導体膜と接する絶縁膜を形成することにより、酸化物半導体膜との界面の状態を良好に保つ。さらに該絶縁膜が、化学量論的組成比より酸素が多い領域を含むことにより、酸化物半導体膜に酸素を供給し、酸化物半導体膜中の酸素欠陥を低減する。また、酸化物半導体膜と接する絶縁膜を積層構造として、酸化物半導体膜の上下に、アルミニウムを含む膜を設けることで、酸化物半導体膜への水の侵入を防止する。

(もっと読む)

液晶表示装置の駆動方法

【課題】画質の低下を防ぎつつ、消費電力の低減を実現することができる、液晶表示装置の駆動方法を提案する。

【解決手段】液晶素子と、当該液晶素子への画像信号の供給を制御するトランジスタとを画素に有する。上記トランジスタは、チャネル形成領域に、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を含み、オフ電流の極めて小さい。そして、画素を反転駆動させる際に、画素電極を間に挟んで配置されている一対の信号線に、互いに逆の極性を有する画像信号を入力する。上記構成により、液晶素子に容量素子を接続しなくても、表示される画質が低下するのを防ぐ。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

光センサ、光センサを搭載した半導体装置、および光センサによる光の測定方法

【課題】リフレッシュ動作を不要とする酸化物半導体を利用した光センサ、当該光センサを搭載した半導体装置、及び光センサを利用した光の測定方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いて形成されたチャネルを含むトランジスタに、ゲート電圧をパルス状に印加することにより、一定のゲート電流が得られることを見出し、これを光センサに応用した。当該光センサはリフレッシュ動作を要さないため、少ない消費電力で、高速かつ簡易な測定手順にて光の照度を測定できる。比較的高い移動度と低いS値、低いオフ電流を有する酸化物半導体を利用したトランジスタにより光センサを形成できるため、少ない工程で多機能を有する半導体装置を得ることが出来る。

(もっと読む)

半導体装置及びその作製方法

【課題】微小なコンタクトホールを形成し、集積回路を微細化することを目的とする。

【解決手段】スイッチング素子および各配線を覆う層間絶縁膜111として有機材料を用い、且つ、金属膜112のマスクを用い、ドライエッチング法によってコンタクトホールを形成し、配線114を形成する。

(もっと読む)

薄膜トランジスタ、その製造方法、及び表示装置並びに電子機器

【課題】製造コストが少なく、光リーク電流が抑制された薄膜トランジスタを提供する。

【解決手段】透明基板上に作製される薄膜トランジスタであって、透明基板上に、少なくともチャネル領域と重畳しないように配置された遮光膜、下地層、結晶性シリコン膜、ゲート絶縁膜、ゲート電極膜を順次形成してなるトップゲート型結晶性シリコン薄膜トランジスタの構造を具え;結晶性シリコン膜には、チャネル長Lのチャネル領域、それを挟むLDD長dのLDD領域、ソース領域、ドレイン領域が形成されており;遮光膜はチャネル領域を挟んで分割されており;分割された遮光膜の間隔xは、チャネル長L以上、チャネル長LとLDD長dの2倍の和(L+2d)以下に選択されていることを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体膜に混入する不純物濃度を制御した活性層を有する半導体回路を備えた半

導体装置を提供するものである。

【解決手段】上記目的を解決するため、ガラス基板上に200nm〜500nmの膜厚の

第1の窒化珪素膜と、前記第1の窒化珪素膜上に第2の窒化珪素膜と、前記第2の窒化珪

素膜上にチャネル形成領域となる領域を含む非晶質半導体膜と、を有する構成において、

前記第1の絶縁膜と前記第2の絶縁膜との界面において、ボロンを有する。

(もっと読む)

電気光学装置及びその製造方法

【課題】液晶装置の画像表示領域のうち非開口領域が占める割合を増大させることなく、画素スイッチング用素子等の半導体素子における光リーク電流を低減する。

【解決手段】凸部42aは、TFTアレイ基板10上において、半導体層1aを覆うように島状に形成されている。遮光膜25は、凸部42aの上面及び側面の夫々に延びている。遮光膜25は、凸部42a及びその周辺までに延びるように大きいサイズの遮光膜が形成された後、凸部42aの上面及び側面に遮光膜25が残るように当該大きなサイズの遮光膜をパターニングすることによって形成されてもよいし、CVD法等の成膜を用いて凸部42aの上面及び側面に成膜されていてもよい。半導体層1aが、3次元的に見てその上側及び側面側の夫々から遮光膜25によって覆われている。

(もっと読む)

電気光学装置及びその製造方法

【課題】例えば、液晶装置の画像表示領域のうち非開口領域が占める割合を増大させることなく、画素スイッチング用素子等の半導体素子における光リーク電流を低減する。

【解決手段】第1層間膜(41)は、第2遮光膜(11)上に形成されている。第1層間膜(41)は、第2遮光膜(11)の形状に対応してTFTアレイ基板10の上方に向かって突出した第1突状部(41a)を有している。このような第1層間膜(41)は、半導体層(1a)の下地になる絶縁膜である。したがって、第2遮光膜(11)上に第1層間膜(41)が形成されるだけで、第1層間膜(41)のうち第2遮光膜11に重なる部分が第2遮光膜(11)の形状に対応した形状を有する第1突状部41aになる。

(もっと読む)

薄膜トランジスタおよび電気光学装置

【課題】半導体層の段切れの発生を防止して製造歩留りを向上できる薄膜トランジスタを提供すること。

【解決手段】TFT素子20は、基板11と、基板11上に形成された遮光層22と、遮光層22を覆う絶縁層24と、絶縁層24上に形成されており、チャネル領域21cを有する半導体層21と、を備え、遮光層22は、半導体層21と平面的に交差する方向に直線状に延在するとともに、チャネル領域21cの少なくとも一部に平面的に重なるように配置された第1の部分22aと、第1の部分22aの延在方向に沿うとともに、半導体層21に平面的に重なるように配置された第2の部分22bと、を有することを特徴とする。

(もっと読む)

電子デバイスおよび電子デバイスの製造方法ならびに電子機器

【課題】画素トランジスタを保護する静電保護素子の特性改質によってリーク電流を低減し、電子デバイスの消費電力を低減すること。

【解決手段】本発明は、絶縁性透明基板101上に互いに交差するように配置された複数の走査線106と複数の信号線107、およびこれら複数の走査線106と複数の信号線107の各交差部に接続される画素TFT102を備えるアクティブマトリクス領域と、アクティブマトリクス領域の外周に配置される周回短絡線104と、周回短絡線104と走査線106および信号線107の少なくとも一方との間に接続される静電保護素子105と、アクティブマトリクス領域の外側に設けられる遮光膜とを備えており、遮光膜の静電保護素子105と対応する部分に開口が設けられているものである。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、画素内のTFTにおける光リーク電流の発生を低減する。

【解決手段】電気光学装置は、基板(10)と、基板上で互いに交差して延在すると共に遮光性の導電膜を夫々含んでなるデータ線(6a)及び走査線(11a)と、データ線及び走査線の交差に対応して設けられた画素電極(9a)と、半導体層(1a)と、基板上で平面的に見て、半導体層における第2の接合領域(1c)を囲う環形状を有し、半導体層におけるチャネル領域(1a’)にゲート絶縁膜(2)を介して対向するように配置されたゲート電極(3a)とを備える。第2の接合領域は、基板上で平面的に見て、データ線及び走査線の交差する交差領域(99cr)内に少なくとも部分的に配置されている。

(もっと読む)

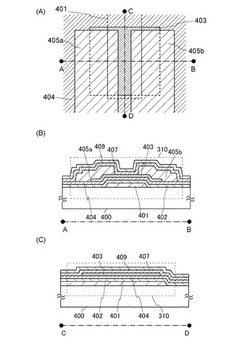

光検出装置および電気光学装置

【課題】不純物導入工程として、N型およびP型のうちのいずれか一方の不純物を導入する工程のみを行なうだけで光センサを形成することのできる光検出装置、およびこの光検出装置を備えた電気光学装置を提供すること。

【解決手段】光検出装置300のセンサ回路310において、主センサ310Aおよび副センサ310Bは、真性領域1xの両側に高濃度N型の第1の不純物導入領域1yおよび第2の不純物導入領域1zが形成された半導体膜1wと、真性領域1xに対して絶縁層4aを介して対向する透光性のバイアス印加用電極5aとを備え、薄膜トランジスタと同一構造を有している。バイアス印加用電極5aに薄膜トランジスタをオフとする方向の電圧を印加するとともに、第1の不純物導入領域1yと第2の不純物導入領域1zとの間に所定の電圧を印加すると、真性領域1xに光が入射した際、光電流が流れる。

(もっと読む)

表示装置

【課題】有機EL素子等の電流駆動型発光素子の経時劣化によっても高品位の表示を行うことができる表示装置を提供する。

【解決手段】画素形成部P(i,j)は、それぞれのゲート端子に接続される制御線Ri,WiおよびゲートラインGiによって制御される第1ないし第4のスイッチ用TFT11〜14は、駆動用TFT15における閾値電圧のばらつきが補償されるよう駆動用TFT15を動作させた後に、そのゲート電位をソースラインSjからの表示映像データの電位で保持されるよう(所定の電圧で)プログラムし、その後有機EL素子16を発光させる。そのとき、有機EL素子16は、その経時劣化によって同じ電圧を与える場合でも輝度が低下するが、第1のコンデンサ17によって駆動用TFT15のゲート−ソース間電圧を所望の値に保つことができるので、高品位の表示を行うことができる。

(もっと読む)

半導体装置

【課題】画像表示機能と画像取り込み機能を同一基板上に備えた半導体装置を提供すること。

【解決手段】半導体装置は、画素マトリクス、イメージセンサ、およびそれらを駆動するための周辺回路を同一基板上に備えている。かつ半導体装置は、イメージセンサの構造・製造プロセスを、画素マトリクスおよび周辺駆動回路の構造・製造プロセスと整合性を持たせることにより安価に作製することができる。また、センサ機能を搭載しても、従来のパネルと基板形状及び大きさは変化しない。そのため、小型化、軽量化することができる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】マスク数を減少させて製造工程を単純化して収率を向上させると同時に、開口率を確保して輝度を向上し得る液晶表示装置およびその製造方法を提供する。

【解決手段】画素部が定義され、該画素部は画素部TFT領域とストレージ領域とに区分される基板201を用意する工程と、該基板201の全面に多結晶シリコン膜205及びストレージ電極膜209を順次形成する工程と、ストレージ電極膜209及び多結晶シリコン膜205を選択的にパターニングして前記画素部を覆う画素パターンを形成する工程と、前記画素パターンのうち、前記画素部TFT領域のストレージ電極膜209を選択的に除去して前記ストレージ領域にストレージ電極209Pを形成すると同時に、前記画素部TFT領域にストレージ電極209Pにより露出された多結晶シリコン膜からなる第1アクティブ層205P1を形成する工程とを備えている。

(もっと読む)

表示装置

【課題】表示パネルに組み込んだ光検知部が明所及び暗所に拘わらず高感度の光検知がで

きるようにした表示装置を提供すること。

【解決手段】アクティブマトリクス基板を有する表示パネルと、前記表示パネルを照光す

る照光手段と、外光を検知する光センサと、所定の基準電圧Vsが充電されるとともに前

記光センサの漏れ電流によって充電された電圧が降下する第1コンデンサCwとを備える

光検知部LS1と、前記第1コンデンサに充電されている充電電圧を所定の読み取り時間

で読み取る光センサ読み取り部Re1と、前記光センサ読み取り部の出力値に基づいて前

記照光手段の制御を行う制御手段と、を備えた表示装置において、前記光センサ読み取り

部は、前記第1コンデンサの充電電圧の電圧降下量に応じて前記読み取り時間を変更する

。

(もっと読む)

半導体装置

【課題】アルミニウム等の材料を用いたトランジスタを高い歩留りで実現するための技術を提供する。

【解決手段】SOI基板またはSIMOX基板に設けられたたタンタル層と、タンタル層上に設けられたアルミニウムまたはアルミニウムを主成分とする材料層とを有し、タンタル層の端部は、アルミニウムまたはアルミニウムを主成分とする材料層の端部より外側に突出し、突出した端部にはタンタルオキサイド層が設けられたトランジスタである。

(もっと読む)

半導体装置及びその作製方法

【課題】回路機能に応じて適切な構造のTFTを配置し、高い信頼性を有する半導体装置を提供する。

【解決手段】基板上に設けられた第1の薄膜トランジスタ及び第2の薄膜トランジスタを有し、第1の薄膜トランジスタ及び第2の薄膜トランジスタは、ソース領域、ドレイン領域、及びチャネル形成領域を含む半導体膜と、半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート配線と、をそれぞれ有する半導体装置において、第1の薄膜トランジスタのゲート絶縁膜を、第2の薄膜トランジスタのゲート絶縁膜よりも厚く設計する。

(もっと読む)

遮光体を具備したトランジスタを有する薄膜回路

薄膜回路は複数の薄膜トランジスタを有し、その各々はソース(72)、ドレイン(70)及びゲート(76)電極から電気的に絶縁された遮光部(60)を有する。遮光部は、第1の、該遮光部がドレイン導体(70)に重なるドレイン重なり部分、第2の、該遮光部がソース導体(72)に重なるソース重なり部分、及び第3の、該遮光部がゲート導体(76)のみに重なるゲート重なり部分を有する。一実施形態において、遮光部の面積の2/3以上はゲート重なり部分から成る。他の一実施形態においては、ソース重なり部分及びドレイン重なり部分の一方は、他方の面積の1.5倍以上の面積を有する。電気的にフローティングの遮光体の使用は層群の構造及び設計を単純化する。この重なり領域の構成は、遮光体とトランジスタ端子との間の静電結合の制御をもたらし、回路性能に影響を及ぼすレベルまで変動する遮光体電圧の影響を抑圧することができる。

(もっと読む)

(もっと読む)

21 - 40 / 43

[ Back to top ]