Fターム[5F110NN72]の内容

Fターム[5F110NN72]の下位に属するFターム

補助容量 (1,949)

Fターム[5F110NN72]に分類される特許

121 - 140 / 3,367

表示装置

【課題】熱処理による特性変動を抑制した酸化物半導体を用いた表示装置を提供する。

【解決手段】実施形態によれば、絶縁層と、絶縁層上のゲート電極と、ゲート電極上にゲート絶縁膜を介して設けられ酸化物層より形成された半導体層と、半導体層の上において、ゲート電極を挟むように離間して設けられたソース電極及びドレイン電極と、を含む薄膜トランジスタと、ソース電極及びドレイン電極のいずれかに接続され、前記酸化物層より形成され前記半導体層よりも電気抵抗が低い画素電極と、画素電極に与えられる電気信号によって光学特性の変化と発光との少なくともいずれかを生ずる光学素子と、画素電極の下に設けられゲート絶縁膜と同じ材料で形成された膜と、を備え、ゲート電極の上のゲート絶縁膜の半導体層の側の表面は、画素電極の下に設けられた膜の画素電極の側の表面よりも平滑性が高い表示装置が提供される。

(もっと読む)

TFT基板の欠陥検査装置及び方法

【課題】TFT基板の材質に依らず、配線やガラスなどのパターン材質の差異を、明瞭に顕在化する欠陥検査装置及び方法を提供する。

【解決手段】TFT基板の配線を通電することにより発熱する短絡欠陥を赤外カメラで検出する欠陥検査装置であって、TFT基板に赤外線を照射する赤外線源と、TFT基板の基準画像を保持する記憶部と、前記赤外カメラで得られた赤外画像と前記基準画像とのマッチングを行う画像処理部とを備え、前記赤外線源は、前記TFT基板から見て前記赤外カメラと同じ側に設置されることを特徴とする欠陥検査装置を提供する。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

π電子共役系化合物前駆体を用いた電子デバイス用インク組成物ならびにその用途

【課題】前駆体膜を変換して得られた半導体膜の導電率の向上。その有機膜を電極と有機半導体の間に配置することで、電極と半導体層の接触抵抗を低減すること。その結果として、接触抵抗が改善された高性能の電気特性を得ることが可能な電子デバイス用インク組成物ならびにそれを用いた電子デバイス、電界効果トランジスタ、およびその製造方法を提供すること。

【解決手段】電子デバイス用インク組成物であって、少なくともπ電子共役系化合物前駆体と、前記π電子共役系化合物のドーパントと、前記π電子共役系化合物前駆体とドーパントを溶解させる溶媒を含有することを特徴とするインク組成物。

(もっと読む)

表示装置および表示装置の製造方法

【課題】酸化物半導体の特性の変化を防ぎつつ、耐圧特性も向上させた薄膜トランジスタを用いた表示装置を提供すること。

【解決手段】表示装置は、薄膜トランジスタを含む。薄膜トランジスタは、ゲート電極と、ゲート電極を覆い絶縁物質を含むゲート絶縁層と、前記ゲート絶縁層の上面に接する酸化物半導体膜と、前記酸化物半導体膜の上面にあり互いに離間する第1の領域と第2の領域にそれぞれ接するソース電極およびドレイン電極と、前記第1の領域と前記第2の領域の間の第3の領域に接し、前記絶縁物質を含むチャネル保護膜と、を含む。平面的にみて前記ゲート電極に重なる前記酸化物半導体膜の上面の領域は第3の領域に含まれかつ小さく、前記酸化物半導体膜のうち前記ゲート電極に重なる部分の一部を除く部分は、前記ゲート電極に重なる部分の前記一部より抵抗が低い。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。

【解決手段】半導体層を酸化物半導体層とする逆スタガ型薄膜トランジスタを含む半導体

装置において、酸化物半導体層上にバッファ層を有する。バッファ層は、半導体層のチャ

ネル形成領域と、ソース電極層及びドレイン電極層とに接する。バッファ層は膜内に抵抗

分布を有し、半導体層のチャネル形成領域上に設けられる領域の電気伝導度は半導体層の

チャネル形成領域の電気伝導度より低く、ソース電極層及びドレイン電極層と接する領域

の電気伝導度は半導体層のチャネル形成領域の電気伝導度より高い。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

表示装置およびその製造方法

【課題】微結晶シリコンを用いたボトムゲート型の薄膜トランジスタのオン電流に対するオフ電流の割合を減少させること。

【解決手段】表示装置に含まれる薄膜トランジスタは、ゲート電極が設けられた導電層と、前記導電層の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上面に接するとともに前記ゲート電極の上方に設けられ、微結晶シリコンを含む第1の半導体膜と、前記第1の半導体膜の上面に接する第2の半導体膜と、前記第2の半導体膜に電気的に接続される第1の電極と、前記第2の半導体膜に電気的に接続される第2の電極と、を含む。前記第1の半導体膜における水素濃度は、前記ゲート絶縁層との界面と前記第2の半導体膜との界面との中間で最小となり、前記第1の半導体膜と前記第2の半導体膜との境界における酸素濃度は、前記第1の半導体膜の中央および前記第2の半導体膜の中央のうち少なくとも一方の酸素濃度以下である。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

液晶表示装置

【課題】オフリーク電流を抑制することが可能な液晶表示装置を提供する。

【解決手段】本発明の液晶表示装置では、半導体層53は、平面視においてゲート電極51の範囲内に配置される。ソース電極55及びドレイン電極57は、平面視において半導体層53の範囲内に配置される。シールド7は、保護絶縁膜4上に配置され、画素電極6と同一の材料からなり、画素電極6と電気的に接続されていない。

(もっと読む)

装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する表示装置を作製する

ための技術を提供する。

【解決手段】固定基板上に、剥離層となる非晶質シリコン膜を介して樹脂基板を形成する

工程と、前記樹脂基板上に少なくともTFT素子を形成する工程と、前記非晶質シリコン

膜にレーザー光を照射することにより、前記非晶質シリコン膜において前記固定基板から

前記樹脂基板を剥離する工程とを行い、前記樹脂基板を用いた柔軟性を有する表示装置を

作製する。

(もっと読む)

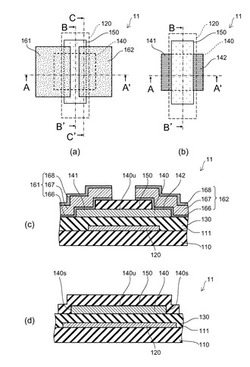

アクティブマトリックス型表示素子およびその製造方法

【課題】少ない工程数でアクティブマトリクス表示素子を形成する。

【解決手段】実施形態にかかるアクティブマトリックス型表示素子の製造方法は、絶縁基板上にゲート電極層、第1の絶縁膜、酸化物半導体層、第2の絶縁膜、酸化物半導体層と電気的に接続したソース・ドレイン電極を順に形成する工程を含む。酸化物半導体層は、ソース・ドレイン電極が形成される領域から画素領域にわたって形成され、第2の絶縁膜を形成する前に、酸化物半導体の画素領域に相当する部分を低抵抗処理して第1の画素電極を形成する。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

液晶表示装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす、適切な構成を備えた保護回路等を提供する。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層104aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に接続するソース電極層またはドレイン電極層との接触抵抗の低減を図る。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層のうち、酸化物半導体層と接する一層104a、104bを薄いインジウム層または薄いインジウム合金層とする。なお、酸化物半導体層103は、インジウムを含む。二層目以降のソース電極層105aまたはドレイン電極層105bの材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

121 - 140 / 3,367

[ Back to top ]