Fターム[5F110NN77]の内容

Fターム[5F110NN77]に分類される特許

41 - 60 / 232

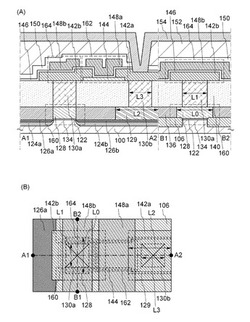

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したゲインセル方式の半導体メモリを提供する。

【解決手段】第1絶縁体101、読み出しビット線102b、第2絶縁体103、第3絶縁体103、第1半導体膜105、第1導電層107a乃至107d等を形成し、その上に凸状絶縁体112を形成する。そして、凸状絶縁体112を覆って、第2半導体膜114a、114bと第2ゲート絶縁膜115を形成する。その後、導電膜を形成し、これを異方性エッチングすることで、凸状絶縁体112の側面に書き込みワード線116a、116bを形成し、凸状絶縁体112の頂部に書き込みビット線125へ接続するための第3コンタクトプラグ124を形成する。このような構造でメモリセルの面積を最小で4F2とできる。

(もっと読む)

半導体メモリ装置

【課題】高度に集積化したDRAMを提供する。

【解決手段】基板201上にメモリセルアレイを駆動するための回路202を形成し、その上にビット線205を形成し、ビット線205上に半導体領域208とワード線210a、210b、キャパシタを形成する。ビット線が半導体領域208の下に位置し、ワード線210a、210b、キャパシタが半導体領域208の上に位置するため、ビット線205の配置の自由度が高まり、オープンビット線型のDRAMとすることで6F2以下、あるいはセルトランジスタの構造を特殊なものとすることで4F2以下とできる。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、電流検出の直線性を向上させられ、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】センスセルの両側にメインセルを配置し、センスセルのエミッタがメインセルのエミッタに挟まれた構造にする。これにより、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけることができ、ミラー比がメインセルとセンスセルそれぞれのエミッタの長手方向における長さの比に近くなる。また、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけられるため、スイッチング時や大電流が流れる時に流れる単位面積当たりの電流量がメインセル側と比較してセンスセル側において大きくなることを抑制できる。このため、電流の偏りを抑制することができ、破壊耐量を向上させることができる。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのスイッチング速度を高速化した半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁層の一部上に形成された半導体層10と、半導体層10の側面10aに形成され、第1のゲート絶縁膜21、第1のゲート電極22、並びにソース及びドレインとなる2つの第1の不純物層23,24を有する第1のトランジスタ20と、半導体層10の側面10bに形成され、第2のゲート絶縁膜31、第2のゲート電極32、並びにソース及びドレインとなる2つの第2の不純物層33,34を有する第2のトランジスタ30とを具備する。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

半導体装置及び表示装置

【課題】複数の有機EL素子への供給電流ばらつきを低減する。

【解決手段】有機EL素子50と電源ラインVLとの間に、電源ラインVLから供給する電流量を制御する素子駆動用TFT20を備え、TFT20のチャネル長方向を、画素の長手方向、又はTFT20を制御するスイッチング用TFT10にデータ信号を供給するデータラインDLの延在方向、又はTFT20の能動層16を多結晶化するためのレーザアニールの走査方向に平行な方向に配置する。さらに電源ラインVLとTFT20の間にTFT20と逆特性の補償用TFT30を備えていても良い。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】DRAMに、高純度化された、バンドギャップが2.5eV以上の酸化物半導体膜、炭化シリコン膜および窒化ガリウム膜などでなるトランジスタを用いることで、キャパシタの電位の保持期間が延びる。また、メモリセルが容量の異なるn個のキャパシタを有し、n個のキャパシタとそれぞれ異なるn本のデータ線を接続することによって保持容量を様々にとることができる。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけられた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとして機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面を有するディスプレイを実現するものである。

(もっと読む)

半導体装置

【課題】複数の有機EL素子への供給電流ばらつきを低減する。

【解決手段】有機EL素子50と電源ラインVLとの間に、電源ラインVLから供給する電流量を制御する素子駆動用TFT20を備え、TFT20のチャネル長方向を、画素の長手方向、又はTFT20を制御するスイッチング用TFT10にデータ信号を供給するデータラインDLの延在方向、又はTFT20の能動層16を多結晶化するためのレーザアニールの走査方向に平行な方向に配置する。さらに電源ラインVLとTFT20の間にTFT20と逆特性の補償用TFT30を備えていても良い。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

41 - 60 / 232

[ Back to top ]