Fターム[5F110PP02]の内容

Fターム[5F110PP02]に分類される特許

61 - 80 / 805

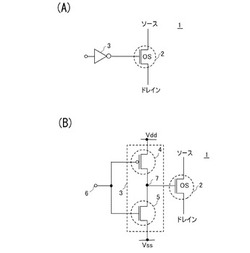

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

イメージセンサ及び電子機器

【課題】後の工程で形成される光電変換層を広く形成することができ、センサの受光面積(開口率)を上げることができる、インテリジェント化された新規な半導体装置を用いた表示装置を提供する。

【解決手段】イメージセンサは、チャネル領域、ソース領域及びドレイン領域を有するトランジスタを有し、トランジスタの上方に絶縁膜を有し、絶縁膜の上方にフォトダイオードを有する。トランジスタはフォトダイオードと重なる位置に設けられている。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼

性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジ

カルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中

の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の

変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

半導体装置

【課題】トランジスタの損傷、破壊の発生を抑制することができる半導体装置を提供する。

【解決手段】第1の基板11上の第1の絶縁層12と、第1の絶縁層上のトランジスタ13と、トランジスタ上の第2の絶縁層14と、第2の絶縁層14に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に接続された第1の導電層15〜18と、第1の導電層上の第3の絶縁層38と、第3の絶縁層38上の第2の基板19と、を有し、トランジスタは、半導体層20と、第2の導電層22と、半導体層20と第2の導電層22の間に設けられた第4の絶縁層21とを有し、第1の絶縁層12、第2の絶縁層14、第3の絶縁層38及び第4の絶縁層21から選択された一つ又は複数は、トランジスタと重ならないように設けられた段差部を有する。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、一対の電流端子を有し、一対の電流端子の一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される整流素子と、を備える。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つ

ソース電極及びドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、加熱処理

を行う。この加熱工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物

半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設け

ることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発

生するのを防止する。

(もっと読む)

フォトセンサの駆動方法、半導体装置の駆動方法、半導体装置、及び電子機器

【課題】小型でコントラストの高い画像データを取得することができるフォトセンサを提供する。該フォトセンサを用いた半導体装置を提供する。

【解決手段】受光素子と、スイッチング素子であるトランジスタと、トランジスタを介して受光素子と電気的に接続する電荷保持ノードとを有するフォトセンサにおいて、導通状態から非導通状態とするためにトランジスタへ供給する駆動パルスの入力波形の立ち下がり時間を遅延させ、電荷保持ノードが保持する電荷の減少を抑制する。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

61 - 80 / 805

[ Back to top ]