Fターム[5F110PP02]の内容

Fターム[5F110PP02]に分類される特許

21 - 40 / 805

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、現在実用化されている量産技術からの膜構成、プロセス条件、または生産装置等の変更が少なく、半導体装置に安定した電気特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、を有し、ゲート絶縁膜は、窒化酸化シリコン膜と、窒化酸化シリコン膜上に形成された酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された金属酸化膜と、を含み、金属酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

表示装置

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

化合物半導体の形成方法

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。

Si基板上のシリコン酸化膜の上に単結晶のSiC膜やGaN膜に形成したMOSFETなどの素子をアニールする手法を開示する。

【解決手段】光学ランプからの光をレンズで集光する手段、或いはレーザ光など高温度を発生させる手段によりSiCなど化合物半導体の表層部はSi基板の融点を越えるような高温度として、Si基板部はその融点よりも十分低い温度となるような冷却部を設けてSi基板を保持するステージを設けたことを特徴とするアニーリング装置。

(もっと読む)

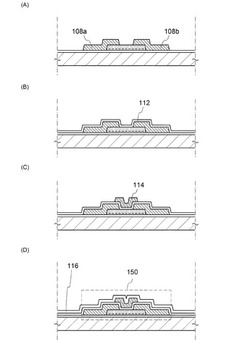

薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、結晶化誘起金属を用いて結晶化された多結晶シリコン層からなり、ソース/ドレイン領域及びチャネル領域を含む半導体層と、前記半導体層上に位置するゲート絶縁膜と、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極上に位置する層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層のソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を含み、前記半導体層は前記半導体層の両端部に位置する第1ゲッタリングサイト及び前記第1ゲッタリングサイトと離隔されて前記半導体層のドレイン領域のみに位置する第2ゲッタリングサイトを含むことを特徴とする薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

(もっと読む)

半導体基材およびその製造方法

【課題】簡便な方法で、結晶化部分を有する半導体基材を得る。

【解決手段】ベース基材と;該ベース基材上に配置された、アモルファス半導体材料由来の結晶性半導体層とを少なくとも含む半導体基材。結晶性半導体層の表面近傍において、SIMSによりGeが検出可能である。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】結晶性の高い酸化物半導体をチャネル層に用いて、優れた特性を有する半導体装置を提供することを課題の一つとする。また、下地膜の平坦性を向上させた半導体装置を提供する。

【解決手段】トランジスタの下地膜に化学機械研磨処理を行い、化学機械研磨処理した後、プラズマ処理を行うことで、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができる。プラズマ処理及び化学機械研磨処理の組み合わせにより得られた平坦性を有する下地膜上に結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置

【課題】半導体装置において生じるTFTのバラツキを低減する。

【解決手段】トランジスタと、第1のソース配線と、隣り合う第2のソース配線と、電源供給線とを有し、第1のソース配線は、トランジスタと電気的に接続することができ、記トランジスタは、チャネル形成領域を有し、チャネル形成領域は、電源供給線と重なる領域を有し、チャネル形成領域は、第2のソース配線と重なる領域を有し、電源供給線は、第2のソース配線と重ならない半導体装置である。その結果、チャネル長Lに対するチャネル幅Wの比が0.1〜0.01であるTFTを提供することができ、各TFT間のバラツキを低減することができる。さらに、電源供給線は第1のソース配線よりも幅の広い領域を有し、電源供給線は、第2のソース配線よりも幅の広い領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを

目的の一つとする。

【解決手段】酸化物半導体層に対して、窒素、または希ガス(アルゴン、ヘリウムなど)

の不活性気体雰囲気下、或いは減圧下で脱水化、又は脱水素化処理のための加熱処理を行

い、酸素、酸素及び窒素、又は大気(好ましくは露点−40℃以下、より好ましくは−5

0℃以下)雰囲気下で加酸化処理のための冷却工程を行うことで高純度化及びI型化した

酸化物半導体層を形成する。該酸化物半導体層を含む薄膜トランジスタを有する半導体装

置を作製する。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

表示装置

【課題】被検出物が表示パネルに非接触の場合でも、被検出物の位置及び動きの検出を行うことを可能とする表示装置を提供する。

【解決手段】表示装置は、フォトセンサ及び酸化物半導体層を含む薄膜トランジスタが配置された表示パネルを有し、被対象物が表示パネルに接近する際に、被検出物が外光を遮ることで表示パネルに投影される被検出物の影がフォトセンサによって検出される。影の位置又は動きを検出することで、被検出物の位置又は動きが検出され、被検出物が表示パネルに非接触の場合でも検出可能となる。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

21 - 40 / 805

[ Back to top ]