Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

681 - 698 / 698

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

SOIおよびバルク・シリコン領域を含む半導体デバイス内のSTI形成

【課題】シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域内にシリコン・トレンチ分離部(STI)を形成する方法、および該方法により形成した半導体デバイスを開示する。

【解決手段】STIは、STIマスクを使用し、バルク・シリコン領域内の所望の深さまでエッチングし且つSOI領域の埋め込み絶縁体で停止する時限エッチングを実行し、SOI領域の埋め込み絶縁体を貫通してエッチングすることにより、SOI領域およびバルク・シリコン領域内で同時にSTIをエッチングすることができる。このプロセスの埋め込み絶縁体のエッチングは、ハードマスク除去ステップの一部として、それほど複雑でなく実行することができる。さらに、バルク領域とSOI領域の両方に同じ深さを選択することにより、その後のCMPプロセスでの問題が回避される。本発明は、窒化シリコンの残留物が存在することがあるSOI領域とバルク領域との境界において不要なものを取り除く。

(もっと読む)

多結晶シリコン薄膜の製造方法、薄膜トランジスタの製造方法、及びシリコン薄膜付き基板

【課題】 非晶質シリコン薄膜に注入された不純物の活性化と非晶質シリコン薄膜の多結晶化とを各々の最適条件の下に一工程で行うことが可能な多結晶シリコン薄膜の製造方法を提供する。

【解決手段】 片面に非晶質シリコン薄膜が形成された電気絶縁性基板を用意し、この非晶質シリコン薄膜上に所定パターンの開口部を有する透光性マスクを形成した後に該透光性マスクの開口部を介して非晶質シリコン薄膜に不純物をドーピングして不純物注入領域を形成し、その後、透光性マスクを残したまま非晶質シリコン薄膜にレーザアニールを施し、不純物注入領域にドーピングされている不純物を活性化して該不純物注入領域を不純物拡散領域にすると共に、非晶質シリコン薄膜のうちで透光性マスクにより覆われている領域を多結晶化することによって、解決した。

(もっと読む)

半導体装置の製造方法

【課題】p型トランジスタの動作速度を高め、n型トランジスタとの動作速度の均衡がとれた半導体装置の製造方法を提供する。

【解決手段】p−MOS領域30aのソース/ドレイン領域にSiGe膜からなる圧縮応力印加部20を形成し、その後にp−MOS領域30aおよびn−MOS領域30bに不純物注入を行い、浅い接合領域22a、22bおよび深い接合領域23a、23bを形成する。SiGe膜を形成する際の加熱により浅い接合領域22a、22bの不純物がゲート絶縁膜15の直下に拡散することを防止し、短チャネル効果を防止すると共に、p−MOSトランジスタ13aのチャネル領域の正孔移動度を高め、n−MOSトランジスタ13bの動作速度との均衡により、相補型の半導体装置10の総合的な動作速度を高める。

(もっと読む)

半導層および絶縁層を形成するために混合溶液を使ってボトムゲート型薄膜トランジスタを形成する改良された方法

【課題】電子デバイスにおいて、ポリマ層を形成し封じ込める。

【解決手段】絶縁性ポリマ層によって保護された半導性ポリマ層を形成する改良された方法を説明する。この方法では、半導性ポリマおよび絶縁性ポリマを形成する物質を溶媒中で溶解する。混合溶液を基板の上に堆積すると、半導性ポリマと絶縁性ポリマとが分離する。溶媒が気化すると、半導性物質はTFTのアクティグ領域を形成し、絶縁性ポリマは、半導性ポリマが空気に露出されることを最小限にする。

(もっと読む)

2つの制御領域を有する集積された電界効果トランジスタ、その使用、およびその製造方法

本発明は、特に、SOI技術およびサリサイド技術により、ダブルゲート・トランジスタ(10)として生成される、電界効果トランジスタ(10)に関する。トランジスタ(10)は、5ボルトよりも高いまたは9ボルトよりもさらに高いターンオン電圧に適し、非常に小さなチップ表面のみを必要とする。トランジスタ(10)は基板領域(14)を有する。基板領域(14)は、2つの電極領域(16、18)と、2つの電気的に絶縁性の絶縁層(100、102)であって、基板領域(14)の対向する面に配置され、制御領域(20、22)に隣接する、絶縁層と、少なくとも1つの電気的に絶縁性の領域(12、110)と、導電性の接続領域(28)、または、1つの電極領域(16)と該基板領域(14)との間の導電性の接続領域の部分(230)とに囲まれる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

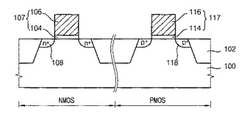

【課題】MOS−FETの駆動力を向上させる高性能な半導体装置及びその製造方法を提供すること。

【解決手段】CMOS−FET回路を備える半導体装置において、NMOS形成領域周辺の素子分離膜(102)の一部に設けられ引張応力を有する引張応力膜(119)と、PMOS形成領域周辺の素子分離膜(102)の一部に設けられ圧縮応力を有する圧縮応力膜(120)と、の少なくとも一方を備えている。

(もっと読む)

薄膜トランジスタを備えた電子装置の製造方法

半導体層(10,20)上部に水素含有層(22)を形成する工程と、半導体層を水素化させるために水素含有層に光照射する工程と、半導体層上部に電極(24、26,28)を形成する工程とを備えた薄膜トランジスタ(42)を備えた電子装置の製造方法。水素が拡散する距離が短くなり、直接的な経路が形成されるので、比較的少ない高レーザフルエンスのレーザパルスを用いた半導体層の高速水素化が可能になる。支持基板(12)はそれ程過熱されないので、この方法は、特に、ポリマー基板上のTFTに有用である。半導体層の結晶化と水素化とを同じ照射工程で行うことができる。  (もっと読む)

(もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

電界効果型トランジスタおよびその製造方法

基体平面から突起した半導体層と、その両側面上に設けられたゲート電極と、ゲート電極と半導体層側面の間に介在するゲート絶縁膜と、第1導電型不純物が導入されたソース/ドレイン領域とを有し、前記半導体層は、ソース/ドレイン領域に挟まれた部分にチャネル形成領域を有し、チャネル形成領域における半導体層上部には、その下方部分より第2導電型不純物濃度が高いチャネル不純物濃度調整領域を有し、このチャネル不純物濃度調整領域は、ゲート電極に信号電圧を印加した動作状態において、当該チャネル不純物濃度調整領域における半導体層のゲート絶縁膜に相対する側面部分にチャネルが形成されることを特徴とする電界効果型トランジスタ。 (もっと読む)

犠牲注入層を用いて非晶質ではない超薄膜半導体デバイスを形成させるための方法

半導体デバイスを形成させるための方法は、単結晶基板(106)の上に犠牲層(108)を定めることを含む。単結晶基板(106)が実質的に非晶質化されないように、ドーパント化学種を犠牲層(108)に注入する。前記ドーパント化学種を前記犠牲層(108)から前記単結晶基板(106)中に移動させるように、犠牲層(108)をアニールする。 (もっと読む)

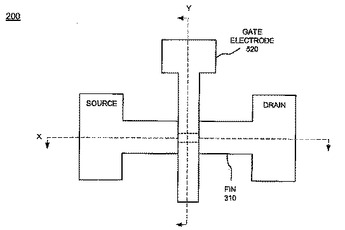

セルフアラインされたダマシンゲート

基板上のフィン領域、ソース領域、およびドレイン領域をパターン化するステップと、フィン領域中にフィン(310)を形成するステップと、フィン領域中にマスク(320)を形成するステップと、を含む、MOS電界効果トランジスタ(MOSFET)(200)を形成する方法である。この方法は、MOSFETのチャネル領域(330)を露出するように、マスク(320)をエッチングするステップと、チャネル領域(330)中のフィン(310)の幅を薄くするようにフィン(310)をエッチングするステップと、フィン(310)上にゲートを形成するステップと、ゲート、ソース領域およびドレイン領域に対するコンタクトを形成するステップと、をさらに含む。  (もっと読む)

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

ダブルゲート電界効果トランジスタ装置を製造する方法、及びそのようなダブルゲート電界効果トランジスタ装置

本発明は、ダブルゲート電界効果トランジスタ装置を製造する方法、及び本方法により形成されるような装置を開示する。セミコンダクタ・オン・インシュレータ基板から開始し、第1のゲート、ソース、ドレイン、及びエクステンションを形成し、第2のゲートを形成する。次に、基板が第2の担体に接合され、半導体層の第2のサイドを露出させる。次に、アニーリングステップが、無拡散アニーリングとして実行される。当該無拡散アニーリングステップには、半導体層が、おおむね一様な厚さを有するだけでなく、おおむね平坦な表面を有する、という利点がある。これによって、前記アニーリングステップについて、実現可能な中で最良のアニーリング作用が確保される。ドーパントの非常に高度な活性化によって、エクステンションの非常にシャープな急峻性が達成される。  (もっと読む)

(もっと読む)

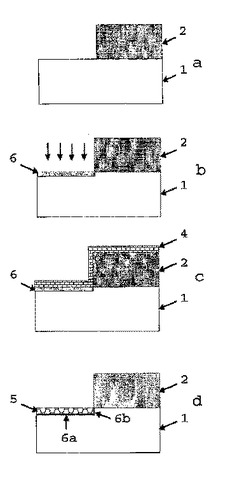

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

681 - 698 / 698

[ Back to top ]