Fターム[5F110QQ30]の内容

Fターム[5F110QQ30]に分類される特許

1 - 20 / 75

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

液晶表示装置及びその不良画素修復方法

【課題】本発明は、液晶表示装置及びその不良画素の修復方法を提供する。

【解決手段】第1の絶縁基板と、第1の絶縁基板上に実質的に第1の方向に互いに平行するように配値されたゲート配線およびストレージ配線と、ゲートおよびストレージ配線と絶縁されて交差し、実質的に第2の方向に配値されたデータ配線と、データ配線上に形成された保護膜と、保護膜上に形成された第1の画素電極と第2の画素電極と、第1の画素電極に隣接する第2の画素電極を含み、ストレージ配線は、実質的に第1の方向に配値された水平部および水平部から実質的に第2の方向に分枝し、データ配線とオーバーラップする垂直部を含み、垂直部は、第1の画素電極および第2の画素電極とオーバーラップし、第1の画素電極と垂直部がオーバーラップする幅は第2の画素電極および垂直部の間のオーバーラップする幅と実質的に同一であることを特徴とする液晶表示装置。

(もっと読む)

電磁波剥離性フレキシブルデバイス用基板およびそれを用いた電子素子の製造方法

【課題】本発明は、安定的に電子素子部を形成可能な電磁波剥離性フレキシブルデバイス用基板を提供することを主目的とする。

【解決手段】本発明は、可撓性を有する金属基材と、上記金属基材の少なくとも一方の表面上に形成された絶縁層と、上記金属基材の他方の表面上に形成され、電磁波剥離性を有する電磁波剥離性粘着樹脂を含む電磁波剥離性粘着層と、を有することを特徴とする電磁波剥離性フレキシブルデバイス用基板を提供することにより、上記目的を達成する。

(もっと読む)

ディスプレイパネルの製造方法

【課題】ショート欠陥部の破片の発生を抑えつつ、かつ確実に配線のショートを解消すること。

【解決手段】薄膜トランジスタを内蔵するTFTパネルと、前記TFTパネルの表面上にマトリクス状に配置され、かつ画素電極を含む画素と、を有するディスプレイパネルの製造方法であって、前記TFTパネルを準備する工程と、前記TFTパネルの表面に画素電極をパターニングする工程と、前記画素電極のショート欠陥部を検出する工程と、前記ショート欠陥部に電圧を印加し、前記ショート欠陥部を溶断する工程と、を有する、ディスプレイパネルの製造方法。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

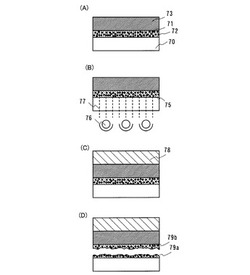

フレキシブル電子デバイスの製造方法および樹脂層付積層基板、ならびにフレキシブル電子デバイス製造部材

【課題】真空プロセスにおける接着層からの脱ガスを抑制するフレキシブル電子デバイスの製造方法、および脱ガスが少ないフレキシブル電子デバイス製造用の樹脂層付積層基板ならびにフレキシブル電子デバイス製造部材を提供する。

【解決手段】寸法安定性に優れた支持基板30に接着層20を介して可撓性基板22を接着した後に熱処理を行うことで接着層20の揮発成分の少なくとも一部を放出させ、かつ接着層20の露出部を覆う樹脂層24を設けることにより、接着層20からの脱ガスを抑制する。

(もっと読む)

半導体素子の製造方法

【課題】粘着材の配置を工夫し、基板を切断して半導体素子を製造することで、粘着力の強い粘着材や熱により硬化する粘着材を使用でき、かつ、製造効率を向上させることができる半導体素子を製造する。

【解決手段】一つ以上の半導体素子を製造する方法において、半導体素子形成領域を基板上に決定する工程と、半導体素子形成領域よりも外側に設定される切断部を決定する工程と、基板の半導体素子形成領域と反対面上で、切断部の外側に粘着材3を積層する工程と、粘着材3上に支持材4を積層する工程と、半導体素子形成領域に半導体素子を積層する工程と、基板上で切断部を切断する工程と、を有する半導体素子の製造方法。

(もっと読む)

デバイスの製造方法

【課題】基板側面に付着した異物の効率的な除去が可能な、デバイスの製造方法を提供する。

【解決手段】基板10Aの側面に保護材3を形成する工程と、基板10Aの少なくとも一方の主面に機能層4Aを形成する工程と、保護材3を基板10Aから剥離する工程と、

を有することを特徴とする、デバイスの製造方法。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

画像表示装置およびその作製方法

【課題】フレキシブルなフィルムまたは金属箔上にTFT素子を形成して軽量化かつ安価な表示装置を提供する。

【解決手段】画像表示素子形成基板として厚さの薄い金属箔を、搬送用金属基板の上に重ねて周囲を溶接する。そして、搬送用基板に固定された薄い金属箔上にTFT素子等を形成して画像表示装置を形成した後、溶接部の内側を切断して画像表示素子が形成された金属箔と搬送用金属基板を分離する。

(もっと読む)

回路基板製造方法

【課題】回路基板製造方法に関し、各レジスト膜又はレイヤーのパターンを適切に検査する方法を提案する。

【解決手段】回路基板200は、基板210に薄膜を形成する薄膜形成工程;薄膜にレジスト膜を形成するレジスト膜形成工程;レジスト膜をマスクとして薄膜を剥離するエッチング工程;レジスト膜を剥離するレジスト剥離工程;を含む一連の工程によって予め定められたパターンのレイヤーを形成し、当該一連の工程が繰り返される。検査工程は、一連の工程において形成されたレジスト膜又はレイヤーのパターンの画像と、次工程以降で形成されるべきレジスト膜又はレイヤーのパターンの情報を含む参照情報とに基づいて、当該一連の工程で形成されたレジスト膜又はレイヤーのパターンを検査する。

(もっと読む)

半導体装置の製造方法、半導体装置及び半導体ウエハへの印字方法

【課題】ウエハの表面に対して垂直方向における位置決めを容易に行うことができ、且つ、ウエハの種別を容易に確認することができる半導体ウエハへの印字方法、半導体装置の製造方法、及び半導体装置を提供する。

【解決手段】絶縁性を有する透明基板及び透明基板の表面上に素子形成膜が積層された構造を有する半導体ウエハを準備する工程と、透明基板の裏面上に位置決め用光を反射する光反射膜を形成する工程と、素子形成膜の配置面側からレーザを照射して光反射膜に印字を形成する工程と、素子形成膜に半導体素子を形成する工程と、素子形成膜及び半導体素子を覆う層間絶縁膜を形成する工程と、コンタクト配線を形成する工程と、メタル配線を層間絶縁膜上に形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

回路基板の欠陥修正方法、回路基板及び半導体装置

【課題】高密度で微細なパターンの断線を低温プロセスによって修正可能な回路基板の欠陥修正方法を提供する。

【解決手段】基板1上に形成された配線3の断線箇所Dを含む基板1の露出面領域に、光照射によって濡れ性が変化する物質を用いた濡れ性調整層5を成膜する。次の第2工程では、濡れ性調整層5における断線個所Dに対応する部分、またはそれ以外の部分に光を照射する。これにより濡れ性調整層5における断線個所に対応する部分の電極形成液に対する濡れ性を、それ以外の部分よりも高くする。その後断線個所Dに対応する濡れ性調整層5部分上に電極形成液を供給して乾燥させる。これにより、断線個所Dに電極形成液を乾燥させた修正電極パターン7を形成する。

(もっと読む)

表示装置

【課題】 アクティブマトリクス型の表示装置の作製工程又は完成品における静電気によ

る不良の発生を抑制する。

【解決手段】 本発明に係る表示装置は、アクティブマトリクス回路の角の部分に隣接し

て、前記アクティブマトリクス回路に接続されていない格子状の放電パターンが形成され

ていることを特徴とする。また、本発明に係る表示装置は、アクティブマトリクス回路の

周辺に、前記アクティブマトリクス回路を構成するゲイト線又はソース線と交わる放電パ

ターンが形成され、前記放電パターンの長さは、前記アクティブマトリクス回路の画素ピ

ッチよりも長いことを特徴とする。これらにより、各種静電破壊によるアクティブマトリ

クス型表示装置の不良の発生を抑制することができる。

(もっと読む)

半導体薄膜の形成方法、半導体薄膜の検査装置および半導体薄膜

【課題】レーザアニールによる結晶化を利用した半導体薄膜の形成において、その結晶化度を従来よりも高精度に評価することが可能な半導体薄膜の形成方法を提供する。

【解決手段】p−Si膜23の結晶化度の検査処理の際に、p−Si膜23およびa−Si膜230へ向けて照射光Loutを照射し、p−Si膜23およびa−Si膜230の透過画像を取得する。画像処理用コンピュータ15において、p−Si膜23(結晶化領域51)の透過輝度とa−Si膜230(未結晶化領域50)の透過輝度との透過コントラストを求める。この際、予め形成された基準マーク6を用いて、結晶化領域51内および未結晶化領域50内におけるコントラスト算出用領域60,61を特定し、これらのコントラスト算出用領域60,61を用いて透過コントラストを求める。そして、求めた透過コントラストに基づいて、p−Si膜23に対する選別を行う。

(もっと読む)

半導体装置用基板の製造方法

【課題】例えばガラス基板の反りの発生を抑制し、信頼性の高い半導体装置用基板を効率的に製造する。

【解決手段】半導体装置用基板の製造方法は、第1素子基板(200a)と第2素子基板(200b)とを、第1基板(20a)における第1半導体素子(30a)が形成された面と、第2基板(20b)における第2半導体素子(30b)が形成された面とが互いに対向するように配置し、接着材(500)を介して互いに貼り合わせる貼合工程と、貼合工程の後に、第1基板における第1半導体素子が形成されていない面、及び第2基板における第2半導体素子が形成されていない面に対して薄板化処理を施す薄板化工程とを含む。更に、第1及び第2基板の各々に支持基板(11)を貼り付ける支持基板貼付工程と、第1及び第2素子基板から接着材を剥離することにより、第1及び第2素子基板を互いに分離する分離工程とを含む。

(もっと読む)

半導体装置及びその製造方法並びに表示装置

【課題】イオン注入領域に形成する薄膜トランジスタ構成層の位置合わせ精度を高めた半導体装置の製造方法を提供する。

【解決手段】半導体膜13上にイオン注入用レジストパターン22Aとアライメントマーク用レジストパターン22Bを同時に形成した後、その全面にイオン注入23し、アライメントマーク用レジストパターン形成部B’以外のレジストパターン22A’を、表面に形成された変質層16をアッシング24した後レジストパターン22A’を除去する。活性化処理25した後、アライメントマーク用レジストパターン22Bを位置合わせの基準にして、半導体膜13をアイランド化するためのレジストパターン26を形成し、それを用いて半導体膜13をアイランド化して半導体部13Aとアライメントマーク9とを形成し、アライメントマーク9を位置合わせの基準にして絶縁膜14、ゲート電極15g、ソース電極15s及びドレイン電極15sを形成する。

(もっと読む)

TFTアレイ検査装置およびTFTアレイ検査方法

【課題】点灯状態を判定するための設定値を、基板種やスキャン条件によって調整することを要することなく、パネルの点灯状態を判定する。

【解決手段】電子線を基板に形成されるパネル上を走査して得られる二次電子を検出することによりパネルのTFTアレイを検査するTFTアレイ検査装置において、パネルのTFTアレイに検査信号を印加して、パネル上に所定パターンの電位分布を形成する検査信号印加手段と、二次電子の検出強度を用いてパネルの点灯状態を判定する信号処理手段とを備える。二次電子の検出強度に対するデータ数から得られる強度分布を求め、この強度分布を正常に点灯した際に得られる強度分布と比較することによってパネルの点灯状態の正否を判定する。この強度分布による判定は基板種やスキャン条件に依存しないため、基板種やスキャン条件が変化した場合であっても判定のための調整は不要である。

(もっと読む)

半導体デバイス内の歪みを正規化する方法及び歪みが正規化された半導体デバイス

【課題】 半導体デバイス内の歪みを正規化する方法及び歪みが正規化された半導体デバイスを提供する。

【解決手段】 この方法は、集積回路の第1及び第2の電界効果トランジスタを形成するステップと、第1及び第2の電界効果トランジスタの上に応力層を形成するステップであって、応力層は第1及び第2の電界効果トランジスタのチャネル領域内に歪みを誘起する、ステップと、第2の電界効果トランジスタの少なくとも一部の上の応力層を選択的に薄層化するステップとを含む。

(もっと読む)

アクティブマトリクス基板及びその検査方法

【課題】画素電極を形成した後の静電気対策及びアレイ検査の双方を実現する。

【解決手段】マトリクス状に設けられた複数の画素電極20aと、各画素電極20aの整列方向の一方向に沿って互いに平行に延びるように設けられた複数の表示用配線18aと、各表示用配線18aの端部にそれぞれ設けられた複数の入力端子20cと、各入力端子20cに導通可能に設けられた短絡配線20bとを備え、各入力端子20cに重なるように圧電素子6aが設けられ、各入力端子20cと短絡配線20bとの間には、短絡配線20bが帯電したときに各入力端子20cと短絡配線20bとを導通状態にすると共に、各入力端子20cが押圧されたときに圧電素子6aからの電気信号により各入力端子20cと短絡配線20bとを非導通状態にするスイッチング素子8aがそれぞれ設けられている。

(もっと読む)

1 - 20 / 75

[ Back to top ]