Fターム[5F140AA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 低雑音化 (29)

Fターム[5F140AA03]に分類される特許

1 - 20 / 29

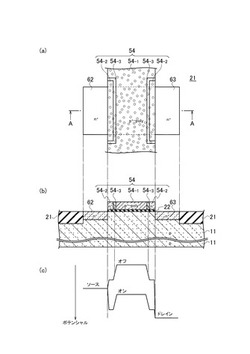

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能する第1導電型の半導体層11、チャネル領域を囲み、半導体層11に活性領域を定義する素子分離絶縁膜21、活性領域の一方に設けられた第2導電型の第1主電極領域62、活性領域の他方に設けられた第2導電型の第2主電極領域63、活性領域の表面のゲート絶縁膜22、多結晶シリコン層を含んで、ゲート絶縁膜22の上に設けられたゲート電極54を備える。多結晶シリコン層は、第1主電極領域62,第2主電極領域63に接する部分は第2導電型の第1多結晶シリコン領域54-2、チャネル領域と素子分離絶縁膜21との境界領域の上部は第1導電型の第2多結晶シリコン領域54-1である。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接するトランジスタ間において、各々のゲート電極の電圧変化の影響が相互に及ばないようにする。

【解決手段】基板100内の素子分離領域220で囲まれた活性領域と、活性領域内に形成された埋め込みゲート電極410a、410bと、埋め込みゲート電極410a、410bの間に設けられ、かつ埋め込みゲート電極410a、410bの底部の深さまで形成された拡散層領域320を有する。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体デバイスおよび方法

低周波雑音の低い微細化素子の製造法とそれを適用した集積回路製品

【課題】MOS集積回路のP型ウェーハ基板やバイポーラ集積回路のNPNトランジスタのベース領域など、N型不純物を添加する以前の下地となるP型領域形成時の特に270〜150℃の範囲の冷却には問題があり、それらの問題を解決し低周波雑音を低減し、平坦性の良い微細化PN接合界面を提供する。

【解決手段】1つ目は下地となるP型領域内の歪エネルギーを最小の状態で固定化することで、2つ目は問題となる素子の近傍に線状欠陥領域を設け、素子の重要な接合部中に発生している格子間シリコンを欠陥のIG能力で吸着せしめる。前者はMOS集積回路の場合は全ての熱処理工程の最初にP型基板を150℃16時間以上、160℃8時間以上等の条件でアニールしておく。このようにすることでP型基板に直接形成するNMOSのチャンネル雑音を低減することが出来る。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

MOSトランジスタ、固体撮像装置、電子機器、及びそれらの製造方法

【課題】チャネル領域の特性向上及び、1/fノイズの改善を図ったMOSトランジスタを提供する。また、そのMOSトランジスタを用いた固体撮像装置を提供する。

【解決手段】ゲート電極31と、ゲート電極31に対して、チャネル領域34が素子分離領域32により複数に分割されたソース・ドレイン領域33から構成されるMOSトランジスタとする。

(もっと読む)

半導体装置

【課題】体格を大きくせずに、スイッチング損失の増大を抑制しつつ、ラジオノイズの発生を抑制することのできる半導体装置を提供する。

【解決手段】半導体基板の表面上に対をなして設けられた第1電極及び第2電極と、第1制御電極とを有し、第1制御電極と第1電極との間に入力される制御信号によって、第1電極と第2電極との間を流れる電流が制御されるトランジスタ素子を備えた半導体装置であって、第1制御電極には、制御信号が入力される部位と、半導体基板におけるチャネル形成領域と対向する領域であって第1電極側の端部との間に第1電位障壁が設けられている。制御信号に応じて、第1制御電極と第1電極との間の容量部の少なくとも一部が、第1電位障壁を介して充放電される。

(もっと読む)

高周波電力増幅器および携帯型無線端末

【課題】動作時の出力低下が少なく、熱雑音の影響が少なく、高周波動作が安定で、かつ信頼性に優れた高周波電力増幅器および携帯型無線端末を提供することを可能にする。

【解決手段】半導体基板上に並列に配置され、それぞれがソース電極、ゲート電極、およびドレイン電極を有する複数のMOSトランジスタと、前記複数のMOSトランジスタのうち隣接するMOSトランジスタ間に設けられた短絡した導体からなる閉ループと、を備え、前記複数のMOSトランジスタのソース電極、ゲート電極、およびドレイン電極はそれぞれ並列に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に複数の半導体素子を有する半導体装置を少ない工程で簡単に製造する。

【解決手段】アナログ回路素子領域25におけるシリコン酸化膜26の表面への窒素導入と、デジタル回路素子領域24におけるシリコン窒化膜27の形成とを、プラズマ窒化法によって同一の工程で行う。そのため、デジタル回路素子領域24のゲート電極パターンとアナログ回路素子領域25のゲート電極パターンとを、同一のフォトリソグラフィ工程によって形成することが可能になる。したがって、互いに異なる組成を有する2つのゲート絶縁膜上の夫々にゲート電極パターンを形成して成る2つのMOS半導体素子を、少ない工程で簡単に形成することができる。また、工程が少ない分だけ加工精度を高めることができる。

(もっと読む)

固体撮像装置とその製造方法、並びに半導体装置とその製造方法

【課題】MOS固体撮像装置における画素のノイズを低減する。白点の発生、1/fノイズの低減を図る。さらに読出し特性の改善を図る。

【解決手段】MOS固体撮像装置における所要の画素トランジスタにおいて、ゲート電極に所要導電型のサイドウォールを形成する。読み出しトランジスタでは、例えばゲート電極63の光電変換素子43側を第1導電型領域63Pとし、フローティングディフージョン部46側を第2導電型領域63Nとして構成とする。好ましくは、ゲート電極63の光電変換素子43側に絶縁膜56を介して第1導電型の半導体材料部64Pを形成する。例えば増幅トランジスタでは、ゲート電極下に埋め込みチャネルを形成し、第1導電型または第2導電型の半導体材料部を形成する。リセットトランジスタでは、ゲート電極のフローティングディフージョン部と電気的に接続される領域側に、所要導電型の半導体材料部を形成する。

(もっと読む)

MOSFETデバイスにおける浮遊体効果を減少させる方法及び構造体

【課題】 シリコン・オン・インシュレータ(SOI)デバイスを含む金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおける浮遊体効果を減少させる方法及び構造体を提供すること。

【解決手段】 電界効果トランジスタ(FET)デバイスは、バルク基板と、バルク基板の上に形成されたゲート絶縁層と、バルク基板に関連する活性デバイス領域内に形成されたソース及びドレイン領域であって、各々が活性デバイス領域のボディ領域に対するp/n接合部を画定するソース及びドレイン領域と、ソース領域内に画定され、ソース領域のp/n接合部を横切ってボディ領域内に至るキャビティの内部に形成された導電性プラグとを含み、ここで導電性プラグはボディ領域とソース領域の間の放電経路を促進する。

(もっと読む)

半導体装置

【課題】半導体基板の表層部にLDMOSが形成されてなる半導体装置であって、微細化が進んでもLDMOSの1/fノイズを十分に低減できる半導体装置を提供する。

【解決手段】第1半導体層3の表層部に形成された第2導電型のソース領域4と、第1半導体層3の表層部にイオン注入により形成され、基板10面内でソース領域4から離間するように配置された第2導電型の第1ドレイン領域5と、第1ドレイン領域5の表層部に形成された、第2導電型で第1ドレイン領域5より高濃度の第2ドレイン領域6とを備え、基板10面内のソース領域4と第2ドレイン領域6を結ぶ最短直線方向において、ゲート電極Gのドレイン側の端面からイオン注入時の第1ドレイン領域5の端面までの距離Wnが、2μm以上に設定されてなる半導体装置100とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ディープウェルを形成する際に半導体基板の浅い領域にイオンが注入された場合でも、そのイオンによるMOSFETへの影響を排除でき、チップ面積の増大を防止することができる。

【解決手段】半導体装置の製造方法において、半導体基板上に露光波長に応じた膜厚のフォトレジストが形成され(S1)、露光波長の光での露光により、第1ウェルの形成領域を開口したフォトレジストパターンが形成され(S2)、形成したフォトレジストパターンをマスクにして、イオン注入により第1ウェルが形成され(S3)、フォトレジストパターンの除去後、半導体基板上にエピタキシャル成長層が形成される(S4)ので、ディープウェルの深さが実質的にイオン注入時よりもエピタキシャル成長層分押し下げられる。

(もっと読む)

半導体装置および半導体基板の製造方法

【課題】オンからオフへの切換時における電圧の跳ね上がりを抑制することができる半導体装置および半導体基板の製造方法を提供する。

【解決手段】シリコン層2において縦方向に延びるN型不純物領域4と縦方向に延びるP型不純物領域5とが横方向に隣接して交互に配置され、オン時に領域4と領域5からなるコラム対における領域4がドリフト層となって電流が流れるとともにオフ時に領域4と領域5との界面から空乏層が広がる。半導体装置のアクティブ領域における、各領域4の幅W4を等しくするとともに各領域5の幅W5を等しくし、さらに、領域4の不純物濃度および領域5の不純物濃度を横方向において場所により異ならせることによってPNコラム対の横方向での不純物面密度を場所により不均一化している。

(もっと読む)

半導体装置およびその製造方法

【課題】膜質が向上したゲート絶縁層を有するMISトランジスタを含む、半導体装置を提供する。

【解決手段】本発明にかかる半導体装置は、半導体層10と、半導体層の上方に設けられたゲート絶縁層20と、ゲート絶縁層の上方に設けられたゲート電極22と、半導体層に設けられたソース領域およびドレイン領域26と、を含み、ゲート絶縁層は、シリコンと、窒素と、重水素とを含有する第1の層20aを含む。

(もっと読む)

線状構造体の配向制御方法、電気素子及び電界効果型トランジスタ

【課題】半導体ナノワイヤ等の線状構造体を配置するときに、その位置やや数量をコントロールする。

【解決手段】基板上にゲート電極と絶縁層が形成された基体を用意し、その上にソース電極11とドレイン電極12を形成する。ソース電極の端部付近に凹凸形成部分24−1とドレイン電極の端部付近に凹凸形成部分24−2を形成し、次にSiナノワイヤ25を分散させた分散液23を、チャネルの中心部分に滴下させる。そして、凹凸形成部分の凹部に分散液中のSiナノワイヤ25を挿入させる。そして、凹部に整列配向したSiナノワイヤ25を、両電極に接合させる。

(もっと読む)

1 - 20 / 29

[ Back to top ]