Fターム[5F140AB07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | バイポーラトランジスタ (89)

Fターム[5F140AB07]に分類される特許

1 - 20 / 89

半導体装置

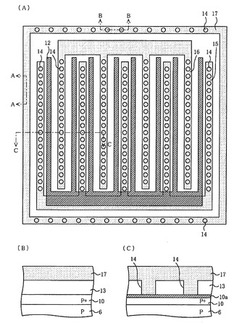

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

半導体装置

【課題】オン抵抗の低減を実現できる、高耐圧のLDMOSトランジスタを有する半導体装置を提供する。

【解決手段】半導体基板上に配置された第2導電型の第1半導体領域と、第1半導体領域の上面の一部に埋め込まれた第1導電型の第2半導体領域と、第2半導体領域の上面の一部に埋め込まれた第2導電型のソース領域と、第2半導体領域と離間して第1半導体領域の上面の一部に埋め込まれた第2の導電型のドレイン領域と、ソース領域とドレイン領域間で第2半導体領域上に配置されたゲート電極と、第2半導体領域とドレイン領域間で第1半導体領域上に配置された絶縁膜と、絶縁膜上に配置されてゲート電極とドレイン領域間の電圧を分圧する分圧素子と、分圧素子とドレイン領域との間に接続された電荷移動制限素子とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

半導体装置設計支援方法、半導体装置設計支援プログラム、及び半導体装置設計支援装置

【課題】バイアス条件によらず、モデルに対する解析精度を向上させる。

【解決手段】本発明による半導体回路の設計支援方法は、第1モデル22を用いて、プロセスパラメータが変動したときのデバイス特性の変動量102を算出するステップと、第2モデル23を用いて算出されたデバイス特性と実測値21との誤差に対して、変動量102で規格化するステップと、演算装置11が、規格化された誤差を用いて第2モデル23に対する解析を行うステップとを具備する。

(もっと読む)

半導体デバイスおよび方法

半導体装置

【課題】 占有面積の増加がなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタのチャネル領域の下部に、濃いN型の不純物を有するシリコン領域からなる埋め込みN型領域を配置した半導体装置とした。

(もっと読む)

半導体装置

【課題】選択素子のビット線方向の長さを短縮する。

【解決手段】半導体装置は、第1導電型の半導体基板10と、半導体基板10に形成された溝に埋設された第1の絶縁膜領域11と、第1の絶縁膜領域11の下面11cを覆うゲート電極WL、ゲート電極WLと半導体基板10の間に設けられるゲート絶縁膜14、を備え、更に、第1の絶縁膜領域11の第1の側面11aを覆う第1の拡散領域15、第1の絶縁膜領域11の第2の側面11bを覆う第2の拡散領域16、及び第2の拡散領域16の上面を覆う第3の拡散領域17とを備え、選択素子は、ゲート電極WL、第1の拡散領域15及び第2の拡散領域16で構成される電界効果トランジスタ、及び基板及び第2及び第3の拡散領域で構成されるバイポーラトランジスタを含む。選択素子の長さが3F(Fは最小加工寸法)で足りるので、埋め込みゲート電極WLを含めて選択素子のビット線方向の長さの短縮が可能。

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

半導体装置

【課題】パワーMOSFETを備える半導体装置のコストの低減を図る。

【解決手段】半導体装置1では、P型の半導体基板2上に、N型の半導体層3が積層されている。そして、半導体装置1は、LDMOS領域5に、ボディ領域8、ドレインバッファ領域9、ソース領域11およびゲート電極14などからなるLDMOSFETを備えている。すなわち、半導体装置1は、LDMOSFETを備えながら、厚膜SOI基板ではなく、N型の半導体層3が直上に設けられたP型の半導体基板2を採用している。そして、フィールド絶縁膜13上に7つのフィールドプレート15が設けられ、そのフィールドプレート15の間隔がボディ領域8側(ソース領域11側)ほど小さくされている。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の拡散によるナローチャネル効果の発生を抑制することを可能にする半導体装置を提供する。

【解決手段】半導体基体1と、半導体基体1に少なくとも一部が埋め込まれた、素子分離のための絶縁層2と、半導体基体1内に形成された不純物領域を含んで成る能動素子と、絶縁層2と半導体基体1との間に形成された、負の固定電荷を有する膜11とを含んで半導体装置を構成する。

(もっと読む)

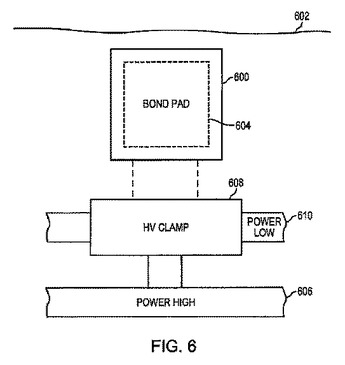

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

1 - 20 / 89

[ Back to top ]