Fターム[5F140AC26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 表面に連続した凹凸を形成するもの (27)

Fターム[5F140AC26]に分類される特許

1 - 20 / 27

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置

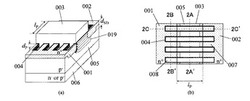

【課題】長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に前記第1トレンチ領域の長さ方向の両端に接して設けられた第2トレンチ領域014および第3トレンチ領域015と、トレンチ領域に形成された第2導電型のウェル領域005と、前記第1トレンチ領域に設けられたゲート絶縁膜004と、前記ゲート絶縁膜上に接して設けられたゲート電極003と、前記第1トレンチと前記第2トレンチ領域と前記第3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

コーナートランジスターとその製作方法

【課題】改善された性能を有し、かつ縮小されたサイズを有することのできるコーナートランジスターを提供する。また、コーナートランジスターを製作する方法を提供し、それがトランジスターの性能を改善するとともに、簡単なプロセスを介して、そのサイズを縮小することができる。

【解決手段】この発明のコーナートランジスターを製作する方法を以下に記述する。分離構造(isolation structure)が基板中に形成されて能動エリア(active area)を定義する。処理プロセスが実施されて、能動エリア中の基板がそのトップエッジに鋭いコーナーを有するようにする。能動エリア中の基板がゲート誘電層により被覆される。ゲート導体がゲート誘電層上に形成される。ソース領域およびドレイン領域がゲート導体両側の基板中に形成される。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

グラファイト薄膜の切断方法、グラファイト薄膜を備える積層基板、およびこれを用いる電界効果トランジスタ

【課題】複雑な加工技術を用いることなく、グラファイト薄膜をナノスケール幅に切断することができるグラファイト薄膜の切断方法を提供すること。

【解決手段】複数の段差部1aを有する基板1の表面に、グラファイト薄膜2を設ける工程と、グラファイト薄膜2が設けられた基板1を、酸素含有雰囲気下で加熱して、グラファイト薄膜2を段差部1aの位置で切断する工程とを含む、グラファイト薄膜の切断方法。

(もっと読む)

半導体装置とその製造方法

【課題】 窒化物半導体層のヘテロ接合を有する半導体装置において、動作温度の上昇に伴うドレイン電流の減少を低減できる半導体装置とその製造方法を提供する。

【解決手段】 HEMT100は、アンドープのGaN層2とn型のAlGaN層4が順に積層されている半導体基板5と、半導体基板5の表面に形成されているソース電極6、ドレイン電極10と、ソース電極6とドレイン電極10の間に形成されているゲート電極8を備えている。半導体基板5の表面には、ソース電極6とドレイン電極10を結ぶ方向に伸びる第1側面12aと、第1側面に直交する方向に伸びる第2側面12bを形成する複数の凹部14群が形成されている。ゲート電極8は、第1側面12aと第2側面12bを被覆している。HEMT100では、メサ型の伝導チャネルが並列に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】所望の位置に不純物領域を精度よく形成することのできる半導体装置およびその製造方法を提供する。

【解決手段】ショットキーバリアダイオードの製造方法は、n型SiC層10を形成する工程と、n型SiC層10の表面にトレンチ30を形成する工程と、トレンチ30を形成する工程の後で、n型SiC層10の表面にケイ素と窒素とを供給した状態でn型SiC層10を熱処理する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上することができるとともに、半導体装置の特性のばらつきを低減することができる半導体装置の製造方法を提供する。

【解決手段】凹凸を有する半導体の表面上に第1イオン注入マスクを形成する工程と、第1イオン注入マスクの表面上に第2イオン注入マスクを形成する工程と、第2イオン注入マスクの表面上にフォトレジストを形成する工程と、フォトレジストの一部を除去して第2イオン注入マスクの表面を露出させる工程と、第2イオン注入マスクの露出部分をエッチングにより除去することによって第1イオン注入マスクの表面を露出させる工程と、第1エッチング工程後に第1イオン注入マスクの露出部分上に残っているエッチング残部をエッチングにより除去する工程とを含む半導体装置の製造方法である。

(もっと読む)

炭化珪素基板の表面処理方法および半導体装置

【課題】より広い幅を有するテラスを形成することができる炭化珪素基板の表面処理方法およびその炭化珪素基板の表面処理方法により表面処理された炭化珪素基板を用いて製造された半導体装置を提供する。

【解決手段】炭化珪素基板の表面上に固体状シリコンを設置する工程と、固体状シリコン上に蓋材を設置する工程と、蓋材の設置後に固体状シリコンが設置された炭化珪素基板を固体状シリコンの融点以上の温度に加熱して固体状シリコンを溶融させる工程と、固体状シリコンの溶融後に固化した固化シリコンから炭化珪素基板を分離する工程とを含む炭化珪素基板の表面処理方法とその炭化珪素基板の表面処理方法により表面処理された炭化珪素基板を用いて製造された半導体装置である。

(もっと読む)

半導体装置および半導体装置を製造する方法

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびそれを製造する方法を提供する。

【解決手段】本発明の半導体装置は、素子分離領域と活性領域を有する半導体装置であって、活性領域とゲート酸化膜が接する第1の面より上に、ソース領域およびドレイン領域の一部が存在し、該ソース領域および/または該ドレイン領域と、該ソース領域および/または該ドレイン領域に電気的に接続される電極とが接する第2の面が、該第1の面に対して傾いている。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域をシリサイド化しても、リーク電流を可及的に抑えることを可能にする。

【解決手段】半導体領域7を有するシリコン基板2と、半導体領域に離間して形成されたソース/ドレイン領域11a、15a、11b15bと、ソース領域とドレイン領域との間の半導体領域上に形成された絶縁膜9aと、絶縁膜上に形成されたゲート電極10aと、ゲート電極の側部に形成された側壁絶縁膜13aと、第1ソース/ドレイン領域上に形成され、少なくとも{111}面となる表面を有する単結晶シリコン層17a、17bと、少なくとも単結晶シリコン層の{111}面上に形成され、かつ側壁絶縁膜に接する部分を有し、この部分と単結晶シリコン層との界面が単結晶シリコン層の{111}面であるNiSi層21a、21bと、NiSi層に接する第1のTiN膜23a、23bと、を有する第1のMOSFETと、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動能力を向上させた半導体装置を提供する。

【解決手段】半導体装置には、ゲート幅方向に断続的に深さの変化する凹部を設けるためのトレンチ部3が形成されており、ゲート絶縁膜6を介して、トレンチ部3の内部及び上面部にゲート電極7が形成されている。ゲート電極7のゲート長方向の一方の側にはソース領域9が形成されており、他方の側にはドレイン領域10が形成されている。ソース領域9とドレイン領域10の少なくとも一部では、ゲート電極7の形成前にトレンチ部3の内壁からイオン注入を用いて不純物添加をおこなった後、拡散および活性化の熱処理を施すことによって、トレンチ部3の表面から底部にかけて深く形成させることを可能とする。これにより、ゲート電極7の凹部上面に集中して流れていた電流がトレンチ部3の全体に一様に流れるようになり、ゲート幅方向に深さが変化するように形成された凹部の実効的なゲート幅が広がる。このため、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

半導体装置とその製造方法

【課題】 高駆動能力横型MOSトランジスタにおいて、単位面積当りのゲート幅を増大させつつ、素子特性の安定した高駆動能力横型MOSトランジスタの構造を提供する。

【解決手段】 MOSトランジスタにおいて、ゲート長方向に対し水平に配置するトレンチもしくはフィンの構造をゲート幅方向に階段状に形成することで半導体基板表面とトレンチ底部もしくはフィン頭頂部の段差が緩和されるため、単位面積当りの駆動能力を上げるために深いトレンチもしくは高いフィンを有している場合においても、イオン注入法を用いてチャネル領域、ソース拡散層およびドレイン拡散層の不純物濃度を均一に形成することができる構造と成る。これにより、チャネルが形成される面による特性の変動が現れない安定した特性が得られ、単位面積当りのオン抵抗が低減された高駆動能力横型MOSトランジスタを提供することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 駆動能力を向上させた半導体装置を提供する。

【解決手段】 当該半導体装置には、ゲート幅方向に深さの変化する凹部を設けるためのトレンチ部8が形成されており、ゲート絶縁膜9を介して、トレンチ部8の内部及び上面部にゲート電極10が形成されている。ゲート電極10のゲート長方向の一方の側にはソース領域12が形成されており、他方の側にはドレイン領域13が形成されている。ソース領域12とドレイン領域13の少なくとも一部の表面は、ゲート電極10近傍にLOCOS法を用いて形成した厚膜酸化膜の除去することで他よりも低く形成する。このように、ソース領域12とドレイン領域13の一部の表面を他よりも低くすることにより、ゲート電極10の当該凹部上面に集中して流れていた電流がトレンチ部8の全体に一様に流れるようになり、ゲート幅方向に深さが変化するように形成された凹部の実効的なゲート幅が広がる。このため、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

1 - 20 / 27

[ Back to top ]