Fターム[5F140BA13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 非単結晶半導体材料 (90) | 多結晶、ポリシリコン (59)

Fターム[5F140BA13]に分類される特許

41 - 59 / 59

複数のチャネルデバイス構造を備えたマルチ動作モードトランジスタ

それぞれ異なる動作特性を有する複数のチャネル(15)が用いられたマルチ動作モードトランジスタが提供される。複数のチャネル(15)は独立に調整可能なしきい値電圧を有する。しきい値電圧を独立に調整することにおいて、少なくとも1つの以下のもの、つまり、異なるチャネル(15)にそれぞれ異なるドーピング濃度、チャネル(15)を分離している異なるゲート誘電体(14a〜14c)にそれぞれ異なるゲート誘電体厚、および、異なるチャネル(15)に異なるそれぞれのシリコンチャネル厚、が供給される。  (もっと読む)

(もっと読む)

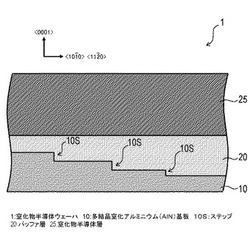

窒化物半導体ウェーハ及び窒化物半導体素子

【課題】多結晶AlN基板を用いつつ結晶性にすぐれた窒化物半導体ウェーハ及び窒化物半導体素子を提供する。

【解決手段】配向性を有する多結晶窒化アルミニウムからなり、主面上に複数のステップ10Sが形成された基板10と、前記基板の前記主面上に設けられた単結晶の窒化物半導体層25とを備えた窒化物半導体ウェーハ1及び前記窒化物半導体層25の上に設けられた電極を備えた窒化物半導体素子。

(もっと読む)

酸化膜の形成方法並びにその酸化膜を備えた半導体装置及びその製造方法

【課題】 半導体基板表面の堆積酸化膜を、高品質、高性能に改質する方法を提供する。

【解決手段】 図1(a)に示すように、被処理用シリコン基板1に二酸化シリコン膜2を形成して、その被処理用シリコン基板1および該二酸化シリコン膜2を処理槽3内の共沸硝酸(沸点120.7℃、濃度68質量%)4などに約1時間浸漬、あるいは酸化性の蒸気への曝露処理をする。これにより、該被処理用シリコン基板1の表面に、通常の高温熱酸化法で形成した二酸化シリコン膜の特性と遜色のない二酸化シリコン膜が容易に形成できる。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

この発明は、ソース−ドレインcMOSトランジスタの置換技術に関する。プロセスは、装置一式を利用して基板材料に窪みをエッチングして、その後、別のものに堆積することに関する。エッチングとその後の堆積とを、大気に曝すことなく、同じ反応器でなす方法が開示される。置換ソース―ドレインアプリケーション用のソース―ドレイン窪みのイン・サイチューエッチングは、現行のエックス・サイチューエッチングに対して幾らかの利点を提供する。トランジスタ駆動電流は、(1)asエッチングされた表面が大気に曝されると、シリコンエピ層界面の汚染が削減されること、(2)エッチング窪みの形状に対する正確制御、により向上する。堆積は、選択的/非選択的方法を含む、様々な技術によりなされてもよい。ブランケット堆積の場合、性能重要領域のアモルファス堆積を避ける基準も提示される。 (もっと読む)

シリコン酸窒化膜及びその製造方法並びにそれを備えた半導体装置

【課題】膜中の欠陥を低減させるとともに、良質で誘電率の高いシリコン酸窒化膜を提供する。

【解決手段】

シアン化合物を、好ましくはアルコール類、ケトン類、ニトリル類及びエーテル類に代表される非水溶媒に溶解させた溶液3中において、半導体基板1に0.5V以上10V以下の電圧を印加して該半導体基板1上に薄膜6を形成することにより、該膜中にシアノ結合を含むシリコン酸窒化膜が形成することができる。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性基材42中に、当該絶縁膜の膜強度を向上させる絶縁性粒子41を含有してなるものである。この絶縁膜は、絶縁性粒子41として、絶縁性基材42の比誘電率と異なる比誘電率の粒子を用いることにより、その比誘電率を調整したものである。例えば、絶縁性粒子41として、絶縁性基材42の比誘電率より低い比誘電率の粒子を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性粒子41の集合体の間隙を、当該絶縁膜の膜強度を向上させる絶縁性の充填物42で充填してなるものである。この絶縁膜は、充填物42として、絶縁性粒子41の比誘電率と異なる比誘電率の材料を用いることにより、その比誘電率を調整したものである。例えば、充填物42として、絶縁性粒子41の比誘電率より低い比誘電率の材料を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

ダイヤモンド電界効果トランジスタ及びその製造方法

【課題】 絶縁耐性が優れたダイヤモンド電界効果トランジスタ及びその製造方法を提供する。

【解決手段】 ダイヤモンド基板1上に、夫々ソース領域及びドレイン領域となる低抵抗ダイヤモンド層2a及び2bを局所的に形成し、これら間及び相互に対向する端部上に、アンドープダイヤモンド又はBが低濃度でドープされたダイヤモンドからなる高抵抗ダイヤモンド層3を形成する。また、低抵抗ダイヤモンド層2a及び2b上に、夫々ソース電極5及びドレイン電極6を形成し、高抵抗ダイヤモンド層3上に、ゲート絶縁膜4を介してゲート電極7を形成する。このとき、ゲート絶縁膜4は、酸化シリコン層、窒化アルミニウム層、アルミナ層、ダイヤモンド状炭素層、窒化シリコン層、ジルコニア層、チタン酸ストロンチウム層、チタン酸バリウム層及びサイアロン層からなる群から選択された2種以上の層を積層した積層膜とする。

(もっと読む)

半導体装置の製造方法

【課題】導通時における駆動力を向上させる。

【解決手段】所定の開口を有するマスク層を用いて、基板1とドレイン領域2からなる半導体基体の一主面側に所定の溝15を形成する工程と、少なくとも溝15の側壁に接して、該溝15からはみ出すように埋め込み領域11を形成する工程と、半導体基体並びに埋め込み領域11に接するようにヘテロ半導体層30を形成する工程と、ヘテロ半導体層30をパターニングし、ヘテロ半導体領域3を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】スイッチング動作における駆動力を向上する。

【解決手段】基板1とドレイン領域2からなる第一導電型の半導体基体の一主面側にヘテロ半導体層30を形成する工程と、所定の開口を有するマスク層をマスクとして用いて、ヘテロ半導体層30を選択的に、かつ所定の厚みを残すようにエッチングする工程と、ヘテロ半導体層30の露出した部分を酸化する工程と、該酸化によって形成された酸化膜10をエッチングしてヘテロ半導体領域3を形成する工程と、ヘテロ半導体領域3並びに半導体基体に接するようにゲート絶縁膜4を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】従来と同等の駆動力を確保しつつ、ヘテロ界面で生じる漏れ電流を低減可能な高耐圧電界効果トランジスタを容易に製造する方法を提供する。

【解決手段】N+型SiC基板1とN−型SiCエピタキシャル層2からなる半導体基体の一主面に接して該半導体基体とはバンドギャップが異なるヘテロ半導体領域3を形成する工程と、該ヘテロ半導体領域3の一部分に、少なくとも半導体基体に達する溝部5を形成する工程と、該溝部5内にゲート絶縁膜6を形成し、該ゲート絶縁膜6に接してゲート電極7を形成する工程と、該ゲート電極7の上部にキャップ絶縁層8を形成する工程と、該キャップ絶縁層8をマスクとして、へテロ半導体領域3に選択的に不純物を導入することで、第一のヘテロ半導体領域9と第二のヘテロ半導体領域10とを形成する工程とを有する

(もっと読む)

応力制御を伴う窒化シリコン膜

アセンブリは、互いに重ねて形成された窒化物エッチストップ層を有する多層窒化物スタックを備え、これら窒化物エッチストップ層の各々は、膜形成プロセスを使用して形成される。多層窒化物スタックを形成する方法は、単一ウエハ堆積チャンバに基板を配置し、堆積の直前に基板に熱的ショックを与えることを含む。第1の窒化物エッチストップ層が基板上に堆積される。第2の窒化物エッチストップ層が第1の窒化物エッチストップ層上に堆積される。 (もっと読む)

半導体装置

【課題】高耐圧化と低オン抵抗化を図ることができる半導体装置を提供する。

【解決手段】半導体基板1上に形成されたpウエル領域であるP−well35と、このP−well35の表面層に形成されるpオフセット領域であるP−off5と、P−off5の表面からP−well35に達するように形成したトレンチ19と、このトレンチ19の側壁にゲート酸化膜20を介して形成したゲート電極21と、トレンチ底に形成した拡張ドレイン領域である拡張ドレイン領域であるN−body6と、このN−body6と接するようにトレンチ19内部上方に向かって形成されたドレイン領域となるnエピタキシャル層30と、Pwell35の表面層に形成したソース領域となる上部のn+ 領域8とで構成する。この構成では、タングステン層23を形成する箇所にドレイン領域となるnエピタキシャル層30を形成するために、トレンチ19を広げることなく、ゲート電極21とドレイン領域となるnエピタキシャル層30の間隔を広げることができるために、高耐圧化と、低オン抵抗化を図ることができる。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

高誘電率誘電材料への酸窒化シリコン層の形成

本発明の実施形態は、基板上に配置された誘電層上にキャッピング層を堆積するための方法を提供する。一例では、プロセスは、基板を堆積プロセスに曝して、この上に誘電層を形成するステップと、該基板をシリコン前駆体および酸化ガスの順次パルスに曝して、堆積プロセス中にシリコン含有層を該誘電層上に形成するステップと、該基板を窒化プロセスに曝して、この上にキャッピング層を形成するステップと、所定の時間該基板をアニーリングプロセスに曝すステップとを含む。該キャッピング層は約5Å以下の厚さを有していてもよい。一例では、該酸化ガスが、触媒を含有する水蒸気生成器によって処理された水素源ガスおよび酸素源ガスから生じた水蒸気を含有する。別の例では、該堆積、窒化およびアニーリングプロセスが同じプロセスチャンバで生じる。 (もっと読む)

複数の狭区画レイアウトを用いたひずみデバイス

大きな引張応力を有する半導体デバイスを提供することを目的とする。半導体デバイスは、ソース領域及びドレイン領域を備える基板を有する。ソース領域及びドレイン領域の各々は、それぞれ、複数の分離されたソース区画及びドレイン区画を含む。シャロートレンチ分離(STI)領域がソース領域の2つの分離されたソース区画間及びドレイン領域の2つの分離されたドレイン区画間に形成される。ゲート積層体が基板に形成される。引張誘起層が基板上に形成される。引張誘起層はSTI領域、ソース領域、ドレイン領域及びゲート積層体を覆っている。引張誘起層は基板に引張応力を生じさせることが可能な絶縁体である。

(もっと読む)

(もっと読む)

高誘電率集積用のシリコンゲルマニウム表面層

高誘電率層(180)を半導体装置中に集積するためにシリコンゲルマニウム(SiGe)表面層(160)を使用する方法である。この方法は、基板(150)上にSiGe表面層(160)を形成し、前記SiGe表面層(160)上に高誘電率層(180)を堆積する。酸化層(170)は、前記高誘電率層(180)とSiGe表面層(160)の未反応部位との間に位置し、前記高誘電率層(180)の堆積中とその後のアニーリング処理中とのいずれか、又はいずれもの間に形成される。前記方法は、前記高誘電率層(180)上に電極層(190)を形成する。  (もっと読む)

(もっと読む)

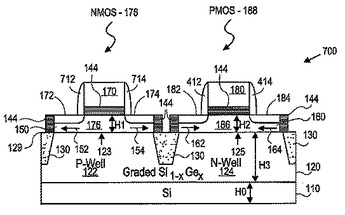

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

41 - 59 / 59

[ Back to top ]