Fターム[5F140BA13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 非単結晶半導体材料 (90) | 多結晶、ポリシリコン (59)

Fターム[5F140BA13]に分類される特許

21 - 40 / 59

半導体基板、半導体装置およびその製造方法

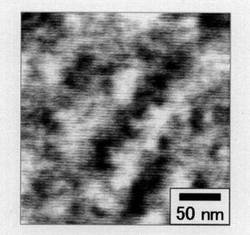

【課題】 (111)表面のシリコン(Si)基板に、原子レベルで超平坦な表面を実現する。

【解決手段】 シリコン基板(111)表面を、予め、フッ化アンモニウム(NH4F)溶液で表面処理した後、濃度68%,沸点120.7℃の共沸硝酸溶液内に浸漬して、前記シリコン基板表面に二酸化シリコン(SiO2)主体の被膜を形成し、ついで、濃度40重量%のフッ化アンモニウム(NH4F)溶液で上記二酸化シリコン(SiO2)主体の被膜をエッチング除去する。AFM像では、バイレイヤー ステップが観測され、表面粗さの指標(RMSラフネス値)が0.07nmと判定され、原子レベルでの超平坦な表面が形成できた。

(もっと読む)

絶縁膜の形成方法及び絶縁膜

【課題】本発明の課題は、絶縁性が良好で、かつ酸化膜換算膜厚のきわめて薄い絶縁膜を提供することである。

【解決手段】水素終端による撥水性を持つシリコン表面から水素原子を脱離させ、親水化したのち、絶縁膜を堆積する工程を含む絶縁膜の形成方法である。

(もっと読む)

半導体装置

【課題】高い動作性能と高い信頼性とを同時に実現しうる新しい構造の半導体装置を提供する。

【解決手段】結晶性半導体で構成されるソース領域101、ドレイン領域103に挟まれた活性領域102において、局所的にゲルマニウムを添加することでSixGe1−x領域105を形成する。このSixGe1−x領域105とゲルマニウムが添加されなかったSi領域106とのバンド構造の差を利用して、ドレイン側からソース側に向かって広がる空乏層を効果的に抑止する。

(もっと読む)

半導体素子

【課題】より大きな電流ノイズを容易に発生させることが可能な半導体素子を提供する。

【解決手段】本発明に係る半導体素子100は、所定の物質により形成されるゲート電極101と、ゲート電極の少なくとも一部を覆うように所定の誘電体を用いて形成されるゲート絶縁膜103と、ゲート絶縁膜上に不純物及び/又は欠陥によるトラップを有する化合物を用いて形成されるチャネル形成領域105と、チャネル形成領域の端部に形成されるソース107/ドレイン109と、を備え、チャネル形成領域の幅は、不純物及び/又は欠陥によるトラップを有する化合物のデバイ長とする。

(もっと読む)

半導体装置

【課題】MIS型半導体装置やMS型半導体装置において、簡便な手法により半導体層の界面準位を所望のエネルギー準位に設定することが可能な半導体装置を提供する。

【解決手段】導電体と、ソース領域とドレイン領域とを有する半導体と、前記ソース領域と前記ドレイン領域との間において、前記導電体と前記半導体とにそれぞれ接して前記導電体と前記半導体との間に設けられた単分子層と、を備え、前記半導体と前記単分子層との界面において、前記単分子層を構成する分子の電子準位が前記半導体のバンドギャップ内に状態密度の極大を形成してなることを特徴とする半導体装置を提供する。

(もっと読む)

半導体デバイスの製造方法

【課題】基板とhigh−k誘電体との界面の品質を最適化する技術を提供する。

【解決手段】high−kゲート誘電体を形成する方法であって、半導体基板を準備する工程と、基板を洗浄する工程と、熱処理を行う工程と、high−k誘電体材料を堆積する工程とを含み、熱処理工程は非酸化雰囲気中で行われて、半導体基板とhigh−k誘電体材料との間に薄い界面層を形成し、薄い界面層の膜厚は10Åより小さい方法。

(もっと読む)

半導体装置およびその製造方法

【課題】素子形成領域間の分離絶縁膜を保護し、接合リークなしに素子と配線膜とを電気的に接続することができる半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1に形成されて素子形成領域2を画定する分離絶縁膜3と、素子形成領域2に形成された素子と、素子および分離絶縁膜3を覆うように半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5をエッチングして形成されたコンタクトホール内に埋め込まれて素子と電気的に接続する配線膜6、7とを備え、少なくとも分離絶縁膜3と層間絶縁膜5との間に、前記エッチングによる分離絶縁膜3の浸食を防止するための3層以上の絶縁膜4a、4b、4cが積層されてなる保護積層膜4が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】高い平坦性の素子分離領域を得ることを課題とする。

【解決手段】トレンチ領域形成用のマスクとしての第1絶縁膜を半導体基板の直上に形成する工程と、マスクを用いて半導体基板にトレンチ領域を形成する工程と、トレンチ領域を含む半導体基板及び第1絶縁膜の直上に第2絶縁膜を形成することで、トレンチ領域上の第2絶縁膜からなる凹部と、第1絶縁膜上の第2絶縁膜からなる凸部と得る工程と、凹部の底面まで凸部を構成する第2絶縁膜を除去する第1除去工程と、第1絶縁膜及び第2絶縁膜を所定の膜厚まで化学的機械研磨法により除去することで、凹部及び凸部より形成された段差を20nm以下に低減する第2除去工程とを含み、第1絶縁膜及び第2絶縁膜が、同一の化学的機械研磨条件で研磨レートに差がない絶縁膜からなり、第2除去工程が、0.2〜0.6重量%の研磨粒子を含むスラリーを用いて行なわれることを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】 チャネル抵抗の上昇を最小限に抑えつつ、トランジスタのコンダクタンス特性に優れた半導体装置を提供する。

【解決手段】 半導体基板上にMOS型トランジスタが形成してある半導体装置において、MOS型トランジスタは、ウェルと逆導電の不純物をチャネルドープすることにより形成されるデプレッション型トランジスタであって、かつ、MOS型トランジスタのチャネル領域が、多結晶シリコン層もしくはアモルファスシリコン層からなる第1のチャネル領域と、単結晶シリコン層からなる第2のチャネル領域と、が順次設けられた積層構造を有しており、更に、第1のチャネル領域が、チャネルドープされた領域とウェルとの境界に形成されるPN接合よりも表面側に位置している。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の製造方法、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難く、高い絶縁破壊耐性(TZDB、TDDBの改善)が経時的に得られるゲート絶縁膜、かかるゲート絶縁膜の製造方法および評価方法、さらに、このゲート絶縁膜を用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】ゲート絶縁膜3は、半導体基板(基材)2上に化学的気相成膜法を用いて成膜され、平均厚さが10nm以下のものであり、シリコン、酸素原子および水素原子で構成され、その密度が2.5g/cm3以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難いゲート絶縁膜、かかるゲート絶縁膜の評価方法を提供する。

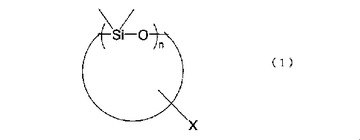

【解決手段】ゲート絶縁膜3は、下記一般式(1)で表される構造を有しており、下記一般式(1)で表される構造中のnが3または4であるものの総数をAとし、nが5以上であるものの総数をBとしたとき、{A/(A+B)}×100が1.2%以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

[式中、nは2以上の整数を表す。また、Xは水素原子または水酸基を表す。]

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

絶縁膜形成方法、絶縁膜形成装置、半導体装置の製造方法、および半導体装置並びにシリコンカーバイドの基板の表面処理方法

【課題】 シリコンカーバイド(SiC)等を用いた半導体デバイスに適用しうる絶縁膜形成において、低温での化学的な酸化膜形成を効果的に行なうための、前処理としての表面処理方法を提供する。

【解決手段】 水素を含む雰囲気中で基板10の表面を加熱した後、その表面を酸化性溶液22中に浸漬し、または酸化性溶液を噴霧し、あるいは酸化性溶液の蒸気に曝す工程を有する。これにより、酸化性溶液22と接触する基板10の表面における反応性の向上が期待でき、その基板10の表面に極薄膜であっても高性能な絶縁膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型トランジスタのカットオフ時のリーク電流を低減する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板と前記半導体基板の内部に形成された第1の不純物拡散領域と前記第1の不純物拡散領域の上方に形成された柱状半導体層と前記柱状半導体層の側方に形成されたゲート絶縁膜と前記ゲート絶縁膜の側方に形成されたゲート電極と前記不純物拡散領域の上方で前記ゲート電極に接して形成された絶縁体からなる層間膜と前記柱状半導体層の上方で前記ゲート電極に接して形成された絶縁体からなるスペーサと前記柱状半導体層の上方に形成された第2の不純物拡散領域とを具備し前記柱状半導体層の略中央に絶縁膜を有する。

(もっと読む)

フィンFETデバイスの構造およびその製造方法

【課題】フィンFET構造およびその製造方法を提供する。

【解決手段】バルク・シリコン基板の上面にシリコンのフィンを形成するステップと、前記フィンの両側の側壁にゲート誘電体を形成するステップと、前記フィンの前記両側の側壁上の前記ゲート誘電体層と直接に物理的にコンタクトするようなゲート電極を形成するステップと、前記チャネル領域の第1の側の前記フィン中に第1のソース/ドレインを形成し、かつ前記チャネル領域の第2の側の前記フィン中に第2のソース/ドレインを形成するステップと、ボイドを生じるために、前記第1および第2のソース/ドレインの少なくとも一部の下方から前記バルク・シリコン基板の一部を除去するステップと、前記ボイドを誘電体材料で以って充填するステップとを含む方法である。構造は、フィンFETのシリコン・ボディとバルク・シリコン基板との間にボディ・コンタクトを含む。

(もっと読む)

応力がかけられたチャネル領域を有する改善されたCMOSデバイス及びそれを製造する方法(半導体デバイスおよび該半導体デバイスの形成方法)

【課題】 同じ応力誘起材料を用いて、n−FET及びp−FET内に異なる応力(すなわち、圧縮及び引張)を生成し、それぞれ内部の電子移動度及び正孔移動度を増大させること。

【解決手段】 本発明は、応力がかけられたチャネル領域を有する改善された相補型金属酸化膜半導体(CMOS)デバイスに関する。具体的には、各々の改善されたCMOSデバイスが、半導体デバイス構造体内に配置されたチャネル領域を有する電界効果トランジスタ(FET)を含み、半導体デバイス構造体は、第1の組の等価な結晶面の1つに沿って配向された上面と、第2の異なる組の等価な結晶面に沿って配向された1つ又は複数の付加的な表面とを有する。こうした付加的な表面は、結晶学的エッチングによって容易に形成することができる。さらに、内因性圧縮応力又は引張応力を有する1つ又は複数のストレッサ層が、半導体デバイス構造体の付加的な表面の上に配置され、かつ、FETのチャネル領域に引張応力又は圧縮応力をかけるように配置され、構成される。こうしたストレッサ層は、半導体デバイス構造体とは異なる格子定数を有する半導体材料の擬似格子整合成長によって形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】寸法制御が容易で特性の安定したLDD構造を有するFETなどの半導体装置の製造方法及びその製造方法によって得られる半導体装置を提供する。

【解決手段】この発明におけるLDD構造を有する半導体装置の製造方法は、レジスト寸法の増大にパターンシュリンク剤を用いる。そして、レジスト3とパターンシュリンク剤6との架橋反応を制御することでLDD構造形成部分の寸法の制御を容易にし、特性の安定した半導体装置を得るものである。

(もっと読む)

半導体装置

【課題】半導体装置の占有面積を低減することを提供することを課題とする。

【解決手段】一対のゲート電極と、共通拡散層と、一対の拡散層と、ボディ部分とを含む一対のDMOSを備え、ボディ部分が、ゲート幅方向における前記共通拡散層の少なくとも一方の端部から延在すると共に、半導体基板主表面上に露出する領域を有することを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

ドープされた半導体物質のエピタキシャル堆積

炭素ドープされたエピタキシャル半導体薄膜(30)の堆積方法であって、露出した単結晶物質(20)を有するパターニングされた基板(10)を収容するプロセスチャンバ(122)内を、約700torrより高い圧力に維持するステップを含む。前記方法はさらに、プロセスチャンバ(122)に、シリコンソースガスのフローを供給するステップを含む。前記シリコンソースガスはジクロロシランを含む。前記方法はさらに、プロセスチャンバ(122)に、炭素前駆物質(132)のフローを供給するステップを含む。前記方法はさらに、露出した単結晶物質(20)上に、炭素ドープされたエピタキシャル半導体薄膜(30)を選択的に堆積するステップを含む。 (もっと読む)

21 - 40 / 59

[ Back to top ]