Fターム[5F140BD18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 断面形状(厚さの不均一性) (541)

Fターム[5F140BD18]の下位に属するFターム

選択酸化(mini_LOCOS) (306)

Fターム[5F140BD18]に分類される特許

1 - 20 / 235

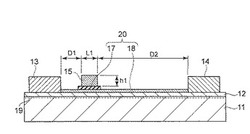

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

半導体装置

【課題】短チャネル効果の抑制およびオフリーク電流の抑制が可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体基板において素子分離領域によって仕切られた素子領域と、前記素子領域を横切る所定の方向に沿って前記素子領域の表層に設けられたゲートトレンチにより分離されて前記素子領域の表層に形成されたソース領域およびドレイン領域とを備える。また、実施形態の半導体装置は、少なくとも一部が前記ゲートトレンチ内にゲート絶縁膜を介して埋め込まれて前記ソース領域およびドレイン領域よりも深い位置まで形成されたゲート電極を備える。ドレイン領域における前記ゲート絶縁膜と接触する界面は、前記ゲート電極側に突出した凸部を有する。

(もっと読む)

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】リセスの下部に形成され不純物の注入量が異なる複数の領域を備える電界緩和層(リサーフ層)を備える半導体装置において、製造工程数の増加を抑えつつ、ディッシングの発生を防止する。

【解決手段】半導体装置は、半導体素子の外周領域であるPウェル2の外縁部に形成されたP型のリサーフ層10を備える。リサーフ層10は、P型不純物が第1面密度で注入された第1リサーフ領域11と、第1リサーフ領域11の外側に配設され、P型不純物が第1面密度よりも小さい第2面密度で注入された第2リサーフ領域12と、第2リサーフ領域12の外側に配設され、P型不純物が第2面密度よりも小さい第3面密度で注入された第3リサーフ領域13とを含む。このうち第1リサーフ領域11および第3リサーフ領域13は、半導体層の上面に形成されたリセス11r,13rの下に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】第2の部分の寄生容量を低下させることにより、半導体装置の特性を向上させる。

【解決手段】MISトランジスタは、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、第1の幅W1を有する第1の部分と第2の幅W2を有する第2の部分とを有するゲート電極を有する。第2の部分の側壁上には、酸化シリコン膜が設けられている。第2の部分に接するゲート絶縁膜は、第1の部分に接するゲート絶縁膜よりも厚くなっている。

(もっと読む)

半導体装置

【課題】 出力回路用、或いは、アナログ回路用の2種類の特性に夫々特性が最適化されてなるトランジスタを備えた半導体装置を低コストで提供する。

【解決手段】

同一基板101上に、出力回路用の第1のトランジスタ1aと、アナログ回路用の第2のトランジスタ1bが搭載された半導体装置であって、各トランジスタのゲート絶縁膜が、ドリフト領域107上面の一部の領域において、膜厚の厚い厚膜絶縁膜108bとなっており、ボディ領域103に向かって延伸するドリフト領域107を、第1のトランジスタ1aでは当該厚膜絶縁膜108bのボディ領域103側境界Aを超えて延伸させ、第2のトランジスタ1bでは当該厚膜絶縁膜108bのボディ領域側境界Aよりも内側にとどまるように延伸させる。

(もっと読む)

半導体装置及びその製造方法

【課題】オン電流が大きい半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、単結晶シリコンからなり、上面が(100)面であり、前記上面にトレンチが形成された基板と、少なくとも前記トレンチの内部に設けられたゲート電極と、前記基板における前記トレンチを挟む領域に形成されたソース・ドレイン領域と、前記基板と前記ゲート電極との間に設けられたゲート絶縁膜と、を備える。前記トレンチは、シリコンの(100)面からなる底面、前記底面に接し、シリコンの(111)面からなる一対の斜面、及び前記斜面に接し、シリコンの(110)面からなる一対の側面により構成されており、前記ソース・ドレイン領域は、前記側面及び前記斜面に接し、前記底面の中央部には接していない。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

1 - 20 / 235

[ Back to top ]