Fターム[5F140BE16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成した後の処理 (810) | 熱処理 (545)

Fターム[5F140BE16]の下位に属するFターム

雰囲気 (347)

Fターム[5F140BE16]に分類される特許

1 - 20 / 198

半導体装置の製造方法

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

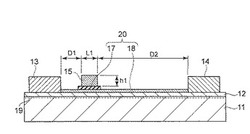

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】EOTの低減及びリーク電流の低減を両立できる半導体装置の製造方法を提供すること。

【解決手段】被処理体上に第1の高誘電率絶縁膜を成膜する第1の成膜工程と、前記第1の高誘電率絶縁膜を、650℃以上で60秒未満の間熱処理する結晶化熱処理工程と、前記第1の高誘電率絶縁膜上に、前記第1の高誘電率絶縁膜の金属元素のイオン半径よりも小さいイオン半径を有する金属元素を有し、前記第1の高誘電率絶縁膜よりも比誘電率が大きい、第2の高誘電率絶縁膜を成膜する第2の成膜工程と、を含む、半導体装置の製造方法。

(もっと読む)

金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置

【課題】ゲート絶縁膜を形成する際に、界面準位を低減しつつ、EOTのさらなる低減が実現可能な金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置を提供すること。

【解決手段】単結晶領域102を有する基板101上に、金属膜であって、該金属膜の酸化物の誘電率が酸化シリコン膜よりも高く、かつ金属膜の酸化物が単結晶領域102とエピタキシャル関係を有する金属膜103を、単結晶領域102と金属膜103とが界面反応しない基板温度で形成する(図1(b))。金属膜103が形成された基板101を、上記界面反応しない基板温度で、単結晶領域102と金属膜103とが界面反応しない酸素分圧の酸素ガス雰囲気に暴露する(図1(c))。酸素ガス雰囲気に暴露された基板103を、上記酸素分圧の酸素ガス雰囲気に保持し、金属膜の酸化物である金属酸化物高誘電体膜が結晶化する基板温度で熱処理する(図1(d)。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

炭化珪素半導体を用いたMOS構造およびその酸化膜形成方法

【課題】 SiO2/SiC界面における界面準位自体を低減することが出来るSiC半導体を用いたMOS構造、およびその酸化膜の形成方法を提供する。

【解決手段】 SiC半導体基板1を処理炉内に用意し、処理炉内を比較的低い700℃に設定して、SiC半導体基板1の基板表面を酸素ガス雰囲気中にさらす。この熱酸化により、SiC半導体基板1の基板表面には、SiO2から成る中間層2が約1nmの極薄い厚さで形成される。次に、中間層2上にSiO2膜を約50nmの厚さに堆積して、SiO2から成る堆積層3を形成する。次に、SiC半導体基板1が酸化しない温度および時間で、堆積層3をアニーリングする。このアニーリングは、赤外線ランプなどの急速加熱装置により、SiO2膜の融点である1200℃に近い、この1200℃の融点よりも低い例えば1000〜1100℃程度の温度で、短時間に急速に行われる。

(もっと読む)

半導体装置の製造方法

【課題】高い誘電率でリーク電流の低い誘電体膜を有する高集積化可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記熱処理後の誘電体膜にイオン化したガスクラスターを照射する照射工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リーク電流および閾値を低減させるゲート絶縁膜を提供する。

【解決手段】図1に示すように、半導体基板1上に、ゲート絶縁膜3を形成するゲート絶縁膜形成工程と、ゲート絶縁膜3上に、ゲート電極4を形成するゲート電極形成工程と、を備え、ゲート絶縁膜形成工程は、第1金属の酸化膜あるいは酸窒化膜を、成膜する第1の成膜工程と、第1金属の酸化膜あるいは酸窒化膜上に第2金属または、その酸化物を成膜する第2の成膜工程と、第2金属を第1金属の酸化膜中に拡散させるために熱処理する熱処理工程の3工程を含む。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のゲートラスト法の問題点を解決し、さらなる微細化に対応できるゲート構造を実現する。

【解決手段】半導体領域101上から、ダミーゲート構造を除去してリセス107aを形成した後、リセス107aの底部の半導体領域101の表面上に界面層108を形成する。次に、界面層108上及びリセス107aの側壁上に高誘電率絶縁膜109を形成すした後、リセス107a内部の高誘電率絶縁膜109上に、ゲート電極の少なくとも一部となる金属含有膜110を形成する。界面層108上に形成されている部分の高誘電率絶縁膜109の厚さは、リセス107aの側壁上に形成されている部分の高誘電率絶縁膜109の厚さよりも厚い。

(もっと読む)

1 - 20 / 198

[ Back to top ]