Fターム[5F140BF07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467) | 金属 (3,194) | 高融点金属 (636)

Fターム[5F140BF07]に分類される特許

621 - 636 / 636

低および高電圧トランジスタを備える半導体デバイスのための方法および装置

【課題】

低および高電圧トランジスタを備える半導体デバイスのための方法および装置を提供する。

【解決手段】

基板は、互いに分けられた低電圧および高電圧領域を備えている。絶縁体を含む分離領域が形成され、このうちには、高電圧領域内におけるウェルのうちの1つに形成される少なくとも1の分離領域も含まれる。高電圧素子領域における活性領域から分離領域の遷移角度は所定の角度よりも大きく、一部実施形態において、それは垂直線に対して40度よりも大きい。一部実施形態において分離領域は、浅いトレンチ分離技術によって形成される。別な実施形態において分離領域は、シリコンの選択酸化技術によって形成されたフィールド酸化膜により作られる。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程を簡略化することができ、低抵抗のソース、ドレインを具備した高性能かつ高信頼性の薄膜トランジスタを有する半導体装置、その製造方法、薄膜トランジスタアレイ基板及び液晶表示装置を提供する。

【解決手段】 導電型が異なる薄膜トランジスタを含んで構成される半導体装置であって、上記薄膜トランジスタは、基板上に半導体層を形成し、この半導体層上にゲート絶縁膜を介してゲート電極を形成し、ゲート電極をマスクにして半導体層に低濃度の不純物を注入して導電型が異なる低濃度不純物領域をそれぞれ形成し、ゲート電極の側面にサイドウォールスペーサーを形成した後に、ソース、ドレイン領域のみに高濃度不純物層としてSiGeを選択的に形成し、一方の導電型の低濃度不純物領域上のSiGeにのみ高濃度不純物層中の不純物とは異なる他の不純物をドーピングし、低濃度不純物領域上に同じ導電型の高濃度不純物領域を形成したものである半導体装置。

(もっと読む)

横型短チャネルDMOS

【課題】 ゲート抵抗およびオン抵抗が低く、高速スイッチング特性および電流駆動特性に優れた横型短チャネルDMOSを提供する。

【解決手段】 P型半導体基体106の表面近傍にはN−型エピタキシャル層110が形成され、その表面近傍にはP型ウェル114およびN+型ソース領域116が形成されている。N−型エピタキシャル層110の表面近傍には、オン抵抗低減用N型ウェル134が形成され、その表面近傍にはN+型ドレイン領域118が形成されている。P型半導体基体106とN−型エピタキシャル層110との境界の、上面から見て少なくともP型ウェル114と重なり合う部分にはN型埋め込み層108が形成されている。また、このN型埋め込み層108の少なくとも一部とN−型エピタキシャル層110とが接するように、N型埋め込み層108の上面を覆うようにP型埋め込み層109が形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

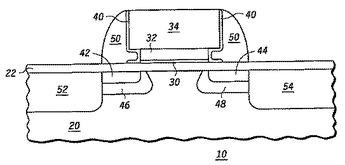

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

半導体構造、二重仕事関数のCMOSデバイス、二重仕事関数のCMOS回路、および基板上に二重仕事関数のCMOSデバイスを形成する方法(炭化金属ゲート構造および形成方法)

【課題】 炭化金属を含むゲート電極を含む少なくとも1つのFETを含む相補型金属酸化膜半導体(CMOS)などの半導体デバイスおよび形成方法を提供することにある。

【解決手段】 このCMOSは、ある金属とある金属の炭化物によって二重仕事関数が与えられる、二重仕事関数の金属ゲート電極を含む。

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

自己制限的界面酸化による超極薄酸化物層および酸窒化物層の形成。

【課題】 自己制限的界面酸化による超極薄酸化物層および酸窒化物層の形成の提供。

【解決手段】 超極薄酸化物層および酸窒化物層は、基板の自己制限的酸化を達成するように、および超極薄酸化物並びに酸窒化物を提供するように、低圧プロセスを利用して形成される。被処理基板は、酸化物層、酸窒化物層、窒化物層、およびhigh−k層のような初期の誘電体層を含むことができるか、あるいは、初期の誘電体層をなくすことができる。プロセスは、バッチ型処理チャンバを使用するか、あるいは、単一のウェーハ処理チャンバを使用することによって、実行されることができる。本発明の一実施例は、厚さ約15ÅのSiO2層をもたらす、Si基板の自己制限的酸化を提供し、そこにおいて、SiO2層の厚さは、基板にわたって約1Å未満で変化する。

(もっと読む)

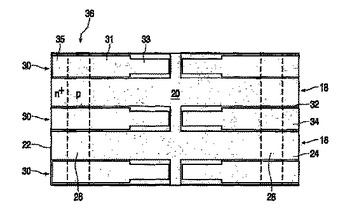

絶縁トレンチゲート電極を有する横型電界効果トランジスタ

縦方向、横方向に交互に配置されたソース領域(22)、ソースボディ領域(26)、ドリフト領域(20)、ドレインボディ領域(28)、およびドレイン領域(24)をそれぞれ有するセル(18)を、減表面電界を達成するための構造とともに有する、電界効果トランジスタである。実施形態における構造は、ソースまたはドレイン領域(22、24)近傍にゲート領域(31)を定義する縦方向に離間された絶縁ゲートトレンチ(35)と、ドリフト領域(20)近傍に縦方向に延在する電位プレート領域(33)と、を含むことができる。代替的に、別個の電位プレート領域(33)または縦方向に延在する半絶縁フィールドプレート(50)をドリフト領域(20)近傍に設けてもよい。このトランジスタは、双方向切り替えに適している。  (もっと読む)

(もっと読む)

621 - 636 / 636

[ Back to top ]