Fターム[5F140BF22]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 4層以上 (153)

Fターム[5F140BF22]に分類される特許

141 - 153 / 153

半導体装置及びその製造方法

【課題】微細化されたゲート電極をCo膜を用いてシリサイド化する場合であっても、ゲート電極の抵抗のばらつきを抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】ゲート長Lgが50nm以下のゲート電極30上に、Co膜72を形成する工程と、熱処理を行うことにより、Co膜72とゲート電極30とを反応させ、ゲート電極30の上部にCoSi膜76aを形成する第1の熱処理工程と、Co膜72のうちの未反応の部分を選択的にエッチング除去する工程と、熱処理を行うことにより、CoSi膜76aとゲート電極30とを反応させ、ゲート電極30の上部にCoSi2膜42aを形成する第2の熱処理工程とを有し、第1の熱処理工程では、CoSi膜76aの幅wに対するCoSi膜76aの高さhの比h/wが0.7以下となるように、CoSi膜76aを形成する。

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】

ポリメタル構造のゲート電極を有するMOSFET、特に、DRAMのメモリセルトランジスタの接合リークをよりいっそう低減する。

【解決手段】

半導体基板上に、ゲート絶縁膜、ポリシリコン膜、タングステンなどの高融点金属膜、ゲートキャップ絶縁膜を順次積層し、エッチングによりゲートキャップ絶縁膜および高融点金属膜を選択的に除去する。その後、ゲートキャップ絶縁膜、高融点金属膜及びポリシリコン膜の側面に、シリコン窒化膜及びシリコン酸化膜からなる2重の保護膜を形成し、これをマスクとして用いてポリシリコン膜をエッチングする。その後、ライト酸化処理を行って、ポリシリコン膜の側面にシリコン酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体装置の製造方法

【課題】 サリサイド工程で形成されるシリサイド層のシート抵抗ばらつきを抑制する。

【解決手段】 サリサイド工程の際にCo膜上に堆積されるTiN保護膜の膜厚を、ナノグレイン構造あるいはアモルファス構造を有するように減少させる。前記TiN保護膜として、Tiに富む組成の膜を使う。

(もっと読む)

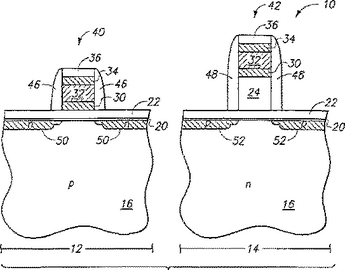

ゲート構造及び該構造を作る方法

【課題】完全なシリサイドゲートを伴うMOSトランジスタの新規構造を得ることである。

【解決手段】本発明は、MOSトランジスタに関し、そのゲートは絶縁層(31)、金属シリサイド層(50)、導電性封入材料層(53)、及びポリシリコン層(55)を連続的に含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のチャネル領域に不純物を注入することのみで閾値電圧を調整するよりも少ない不純物量で電界効果型トランジスタの閾値電圧を調整する。

【解決手段】 半導体装置100は、シリコン基板101と、シリコン基板101上に形成されたSiON膜113および多結晶シリコン膜106を含むP型MOSFET103を備える。多結晶シリコン膜106とSiON膜113との界面115に、Hf、Zr、Al、La、Pr、Y、Ti、TaおよびWからなる群から選択される一または二以上の金属が存在する構成とし、界面115における当該金属の濃度を5×1013atoms/cm2以上1.4×1015atoms/cm2未満とする。

(もっと読む)

半導体装置とその製造方法

【課題】シリコン窒化膜を堆積してもシート抵抗が上昇しない配線構造を提供する。

【解決手段】半導体基板上に第一の高融点金属膜5を形成する工程と、前記第一の高融点金属膜上に高融点金属窒化物の反応物7を持つ第二の高融点金属膜6Aを形成する工程と、前記第二の高融点金属膜上にシリコン窒化膜8を形成する工程とからなる。これにより、シリコン窒化膜の膜質を変化させることなく、また成膜時のパーティクルの発生を従来方法と同等としたまま、シリコン窒化膜下の高融点金属のシート抵抗の上昇を最小限に抑えることができる。

(もっと読む)

ポリシリコンゲルマニウムゲートスタック及びその形成方法

従来のCMOSゲートスタックと比べて反転キャパシタンスを増大させるCMOSゲートスタックが記載される。ゲート誘電体層に近い従来のポリSiゲートの代わりに、ポリSiGeゲートを用いて、活性化され得る埋込まれたドーパント量を増加させる。この増加は、従来のCMOSゲートスタックにおける反転キャパシタンスを制限するポリシリコンの枯渇を克服する。ポリSiGe層をゲートスタックに組込むために、ゲート誘電体層とポリSiGe層との間にSi薄層を堆積させる。適切なサリサイド形成を確実にするために、ポリSiGe層の上にポリSi層のキャップを被せる。ポリSiGeの上に微粒子のポリSiを得るために、ポリSi層とポリSiGe層の間に第2のSi層を堆積させる (もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

タングステンシリサイド薄層の堆積とゲート金属の組込み

ゲート電極の層を堆積させる方法が提供される。その方法には、ドープされた多結晶シリコン層と、タングステンシリサイド薄層と、金属層とを堆積させるステップが含まれる。一態様においては、ドープされた多結晶シリコン層とタングステンシリサイド薄層は集積処理システム内に堆積される。他の態様においては、タングステンシリサイド層を堆積させるステップには、多結晶シリコン層をシリコン源に曝す工程と、タングステンシリサイド層を堆積させる工程と、タングステンシリサイド層をシリコン源に曝す工程とが含まれる (もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

141 - 153 / 153

[ Back to top ]