Fターム[5F140BF22]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 4層以上 (153)

Fターム[5F140BF22]に分類される特許

41 - 60 / 153

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体素子及びその製造方法

【課題】ソース・ドレイン電極及び/又はゲート電極の低抵抗化を図り、微細化・高集積化を損なうことなく、低消費電力で高速操作可能な半導体素子を提供する。

【解決手段】素子分離領域102によりシリコン基板101A表層に画成された素子領域に、チャネル領域を隔てて形成された一対のソース・ドレイン領域106と、ソース・ドレイン領域のそれぞれに導通するソース・ドレイン電極と、チャネル領域上にゲート絶縁膜103を介して形成されたゲート電極と、を備えた半導体素子において、ソース・ドレイン電極及び/又はゲート電極を、ソース・ドレイン領域表面又はゲートを構成するポリシリコン層表面に形成した第1金属膜がシリサイド化されてなるシリサイド層107bと、このシリサイド層上に無電解メッキ法により形成された第2金属膜108と、で構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】デュアルゲート電極構造のMOSトランジスタにおいて、閾値電圧シフト及びばらつきを抑えることができる半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板上にP型MOSトランジスタ及びN型MOSトランジスタを備える半導体装置において、P型MOSトランジスタ及びN型MOSトランジスタは、それぞれチャネル極性と同極のポリゲート電極を備えたデュアルゲート構造のMOSトランジスタであって、デュアルゲート型MOSトランジスタのポリゲート電極が、ゲルマニウムからなる第1のポリゲート電極層と、ゲルマニウムとシリコンとが混在した第2のポリゲート電極層と、シリコンからなる第3のポリゲート電極層と、を順次備えた積層構造を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】キャップ膜としてのランタン酸化膜の膜厚の増加を抑えつつ、閾値電圧の低減化を図れる、窒化チタン膜を含むメタルゲート電極/Hfを含有するゲート絶縁膜のゲートスタック構造を有するMOSFETを備えた半導体装置を適用すること。

【解決手段】P型半導体領域105を含む半導体基板101と、P型半導体領域101に形成されたNチャネルMOSFETとを具備してなり、前記NチャネルMOSトランジスタは、半導体基板101上に形成され、ハフニウムを含有するゲート絶縁膜108と、ゲート絶縁膜109上に形成され、膜厚が所定値以下のランタン酸化膜109と、ランタン酸化膜109上に形成され、N/Ti原子数比が1未満の窒化チタン膜110を含むゲート電極とを具備してなることを特徴とする。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置及びその製造方法

【課題】nMOS及びpMOSの双方において低い閾値電圧を実現することができ、製造コストが低い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上の全面にシリコン酸窒化膜5を形成し、シリコン酸窒化膜5上にランタン酸化膜6を形成し、pMOS領域RpMOSからランタン酸化膜6を除去する。次に、全面に高誘電率膜である窒化ハフニウムシリケイト膜7を形成し、アルミニウム含有窒化チタン膜8を形成し、ポリシリコン膜9を形成し、これらの積層膜をゲート電極形状に加工する。次に、ソース・ドレイン領域12及び13に不純物を導入し、これらの不純物を活性化させるアニール処理を利用して、アルミニウム含有窒化チタン膜8中に含まれるアルミニウムを、pMOS領域RpMOSにおけるシリコン酸窒化膜5と窒化ハフニウムシリケイト膜7との界面まで拡散させる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】NMOSFET及びPMOSFET等のNMOS及びPMOSを有する半導体装置において、ゲート電極の実効仕事関数を、Siバンドギャップのmid-gap付近の値に安定的に設定することが可能な半導体装置及びその製造方法を提供する。

【解決手段】素子分離膜によって分離されてなる、p型拡散層及びn型拡散層を有する半導体基板と、前記半導体基板の、前記p型拡散層及びn型拡散層それぞれの上に形成されてなるゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属膜を含むゲート電極と、前記ゲート絶縁膜と前記金属膜との界面に形成されたGe介在物と、前記金属膜上に形成されたシリコン含有層と、を具えるようにして半導体装置を構成する。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

アルミニウムがドープされた金属炭窒化物ゲート電極の作製方法

半導体デバイス用のアルミニウムがドープされた金属(タンタル又はチタン)炭窒化物ゲート電極の作製方法が記載されている。当該方法は、上に誘電層を有する基板を供する工程、及びプラズマが存在しない状態で前記誘電層上に前記ゲート電極を作製する工程を有する。前記ゲート電極は、金属炭窒化物を堆積する堆積工程、及び前記金属炭窒化物上にアルミニウム前駆体の原子層を吸着させる吸着工程によって作製される。前記堆積工程及び前記吸着工程は、前記アルミニウムがドープされた金属炭窒化物ゲート電極が所望の厚さを有するまで、必要な回数だけ繰り返されて良い。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

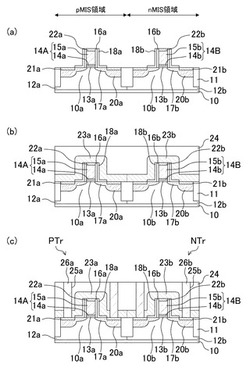

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

成膜装置及び成膜方法

【課題】 ドーパントの活性化率の高いシリコンゲルマニウム膜を成膜するにあたり、シリコンゲルマニウム膜のマイグレーションを抑えること。

【解決手段】 反応容器内に処理ガスを供給すると共に処理雰囲気の温度を所定の温度に設定して基板上にシリコンゲルマニウム膜を成膜する工程(P4)と、次いで反応容器内に水素ガスを供給してシリコンゲルマニウム膜をアニールする工程(P5)と、その後、反応容器内を真空排気し続いてパージガスによりパージする工程を1回行うかまたは複数回繰り返す工程(P6)と、しかる後に基板を反応容器内から搬出する工程(P7)と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】Hf及びZrの少なくともいずれかを含むゲート絶縁膜の膜質を安定させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体層と、半導体層の上に設けられ、Hf及びZrの少なくともいずれかを含むゲート絶縁膜と、ゲート絶縁膜の上に設けられ、Hf及びZrの少なくともいずれかを含む炭窒化物を含むゲート電極と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

41 - 60 / 153

[ Back to top ]