Fターム[5F140BG01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ダミーゲートを用いたゲート電極の製造 (506)

Fターム[5F140BG01]の下位に属するFターム

ダミーゲート材料(レジスト、ポリイミド) (470)

Fターム[5F140BG01]に分類される特許

1 - 20 / 36

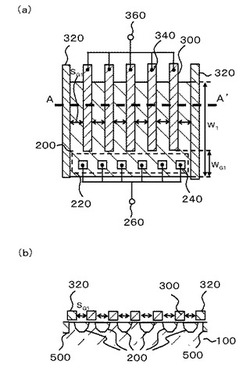

半導体装置及び半導体装置の検査方法

【課題】狭いゲート電極間にコンタクトを配置することなく、オーバーラップ容量を測定する。

【解決手段】この半導体装置は、下記のような第1TEGパターン(不図示)を備えている。第1TEGパターンは、素子分離領域500と、素子分離領域500に形成された開口部(不図示)と、開口部上に設けられ、互いに平行に延伸した複数のゲート電極300と、開口部のゲート電極300で覆われていない部分に形成された拡散領域200と、を備えている。ここで、ゲート電極300の一方の端部は、開口部の外縁よりも内側に配置されている。また、第1コンタクト240は、ゲート電極300の一方の端部と、開口部の外縁の間に位置して、拡散領域200に接続している。一方、第2コンタクト340は、ゲート電極300に接続している。

(もっと読む)

半導体装置の製造方法、並びにデータ処理システム

【課題】チャネル領域を拡大することが可能な半導体装置の製造方法を提供する。

【解決手段】素子分離用の溝部3を形成した後、素子分離絶縁膜4として、当該溝部3に埋め込まれた状態で基板2の面上を覆うシリコン酸化膜26,31を形成する工程と、シリコン酸化膜26,31上に少なくとも埋め込みゲート用の溝部10を形成する位置に開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部を通してシリコン酸化膜31を異方性エッチングにより選択的に除去することによって、当該シリコン酸化膜31に第1の溝部9と同じ幅及び深さとなる第2の溝部10を形成する工程と、第2の溝部10の底面及び側面に位置するシリコン酸化膜26,31を等方性エッチングにより選択的に除去することによって、当該第2の溝部10を活性領域6に形成される第1の溝部9よりも深く、且つ、第1の溝部9よりも大きい幅とする工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体装置

【課題】トランジスタ対を有する半導体装置において、回路面積の増大を抑えつつ、対をなすトランジスタの特性のアンバランスを抑制する。

【解決手段】トランジスタ1a,1bは活性領域パターンが互いに同一である領域A1a,A1bを有し、トランジスタ2a,2bは活性領域パターンが互いに同一である領域A2a,A2bを有する。トランジスタ2a,2bの活性領域13a,13bは、チャネル長方向の長さがトランジスタ1a,1bの活性領域11a,11bよりも長く、領域A2a,A2bは領域A1a,A1bよりもチャネル長方向の幅が狭い。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置

【課題】MIS型半導体装置やMS型半導体装置において、簡便な手法により半導体層の界面準位を所望のエネルギー準位に設定することが可能な半導体装置を提供する。

【解決手段】導電体と、ソース領域とドレイン領域とを有する半導体と、前記ソース領域と前記ドレイン領域との間において、前記導電体と前記半導体とにそれぞれ接して前記導電体と前記半導体との間に設けられた単分子層と、を備え、前記半導体と前記単分子層との界面において、前記単分子層を構成する分子の電子準位が前記半導体のバンドギャップ内に状態密度の極大を形成してなることを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

高周波用トランジスタ

【課題】 ゲートフィンガーに対する寄生キャパシタを小さくして高周波特性の向上をはかることができ、且つ歩留まりの向上をはかる。

【解決手段】 真性領域部10にドレインフィンガー12とソースフィンガー13とを交互に配置し、隣接するドレインフィンガー12とソースフィンガー13との間にゲートフィンガー11を設けた高周波用トランジスタであって、真性領域部10の外側にゲートフィンガー11の複数本毎に分離して設けられ、各々がゲートフィンガー11の片側端部に接続されて、ゲートフィンガー11を複数本ずつ接続する複数のゲート接続用半導体層21と、複数のゲート接続用半導体層21上に連続して形成され、各々のゲート接続用半導体21層にそれぞれ複数のコンタクト23で接続されたゲート接続用配線メタル層22とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】高速かつ低消費電力、高記憶密度な半導体装置の製造方法を提供する。

【解決手段】半導体基板中のp型およびn型ウェル上にLa、Al、Oからなる第1および第2非晶質絶縁膜をそれぞれ形成し、第1、第2非晶質絶縁膜上に、その酸化物標準生成エンタルピーの絶対値が第2非晶質絶縁膜の酸化物標準生成エンタルピーの絶対値よりも小さい第1ゲート電極を形成し、その後形成された構造体全体を酸素雰囲気で熱処理し、その後、第1ゲート電極上に金属膜を形成し、第1ゲート電極と金属膜を固相反応させ、第2ゲート電極を形成する。

(もっと読む)

半導体装置

【課題】高耐圧で、安全動作領域が広く、かつ、熱散逸性がよく、有効コンダクタンスおよび周波数特性が良好なSOIデバイスを提供すること。

【解決手段】半導体装置100において、p-基板101の表面層の一部にはBOX領域102が設けられる。BOX領域102は、ゲート構造部130の中心から下ろした垂線Lc付近まで設けられており、ドレイン領域112および拡張ドレイン領域108をp-基板101から分離する。ドレイン領域112の厚さは150nm〜300nmのいずれかであり、BOX領域102の厚さは150nm以上である。

(もっと読む)

半導体装置、およびその製造方法

【課題】適切なトランジスタ閾値電圧を与えるメタルゲート電極を有し、比較的簡単な製造工程により製造することのできる半導体装置、およびこれを実現可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置は、シリコンを含む半導体基板と、前記半導体基板上に形成された比誘電率が8以上の高誘電材料からなる第1、および第2のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成されたジャーマナイドからなる第1のゲート電極と、前記第2のゲート絶縁膜上に形成されたシリサイドからなる第2のゲート電極と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高性能化が必要な回路ブロックや回路部に対して応力を付加することにより、その回路ブロックや回路部の高性能化が実現できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体チップ基板30内に少なくとも金属酸化物半導体(MOS)トランジスタ36を含む回路と、この回路を含み、上部にこの回路を保護する保護膜41で覆われた回路ブロックを複数有してなる半導体装置20であって、この半導体装置20の電流能力およびしきい値電圧が所定の値を満たさない高性能化が必要な回路ブロックの上部のみに、少なくとも保護膜41を介して複数のバンプ23a、23b、23cが形成され、この複数のバンプ23a、23b、23cはMOSトランジスタ36に応力を付加して移動度を増加させて高性能化が実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の問題が生じることのないソース・ドレイン領域を有する。

【解決手段】半導体装置25は、半導体基板10上に一定間隔で列状に形成された多数のMOSFET用の複数の柱状ゲート電極16と、複数の柱状ゲート電極16のうちの隣接する2つの柱状ゲート電極間の一部分に形成されるMOSFETのチャネルに相当する半導体領域19と、を備える。この半導体装置の製造方法は、半導体基板を含む基層10〜12の表面に複数の穴14を列状に形成し、これら列状の複数の穴14に半導体を埋め込んで柱状ゲート電極16を列状に複数形成し、ゲート電極16の少なくとも一部を露出させて半導体基板10,11の表面に複数の柱状ゲート電極16を露出させ、隣接する2つの前記柱ゲート電極の離隔する距離の半分の長さよりも厚い絶縁物からなるゲート側壁膜17を成膜し、列状で複数の柱状ゲート電極16の上端を平坦面としてから金属膜により橋絡して第2ゲート電極23を形成し、ゲート電極を製造する。

(もっと読む)

半導体デバイス

【課題】従来は、シリコンのバンド構造を十分に変調できず、十分に大きな移動度を持つチャネルが形成できない。四面体構造を有する半導体を母体材料として、構成物質の置換、格子間位置への物質導入を行い、より高移動度の半導体チャネル材料及びそれを用いた電子素子を提供することにある。

【解決手段】構成原子が四面体結合構造を成して結合する母体半導体に、格子点サイトの構成原子と置換される不純物原子Sと、格子間サイトに挿入される不純物原子Iとを含み形成される。不純物原子Sと不純物原子Iとの間の電荷移動により、不純物原子Sが母体半導体の構成原子と一致した電荷を持ち、不純物原子Iが閉殻構造の電子配置をとった状態で結合している半導体物質をチャネル材料に用いることで、高移動度且つ、高電流駆動力を有する電子素子である。

(もっと読む)

デュアル応力ライナ技術におけるデバイス性能の変動を改善するための方法及び構造体

【課題】 集積回路の全体寸法を著しく増大させることなく、デュアル応力ライナ境界問題を克服する方法及び半導体構造体を提供すること。

【解決手段】 本発明によれば、デュアル応力ライナ境界又はその間のギャップは、隣接するダミー・ゲート領域上に強いて置くようにされる。隣接するダミー・ゲート領域上にデュアル応力ライナ境界又はギャップを強いて置くようにすることによって、デュアル応力ライナ境界又はギャップに関連する大きな応力が、半導体基板にではなくダミー・ゲート材料に移行する。したがって、最も近くに隣接するFETに対するデュアル応力ライナ境界の影響が低減される。さらに、本発明を用いてデバイス変動性及びパッキング密度の利点が達成される。

(もっと読む)

1 - 20 / 36

[ Back to top ]