Fターム[5F140BH28]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | ソース、ドレイン材料 (598) | 多結晶 (39)

Fターム[5F140BH28]に分類される特許

1 - 20 / 39

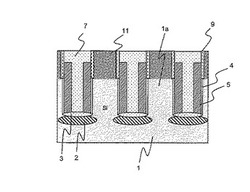

半導体装置の製造方法

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の大きさを大きくすることなく、増幅率の向上と、高耐圧化を図ることを課題とする。

【解決手段】基板上にドレイン部,ゲート部およびソース部が形成され、ゲート部は、基板上に形成されたゲート絶縁膜と、その上に形成されたゲート電極とからなり、ドレイン部は、ゲート電極の一方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ドレイン領域と、より表面近傍に形成された中間濃度ドレイン領域と、基板の上の高濃度ドレイン領域とからなり、ソース部は、ゲート電極の他方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ソース領域と、より表面近傍に形成された中間濃度ソース領域と、基板上の高濃度ソース領域とからなり、高濃度ソース領域は、ゲート電極の上方であって基板表面に平行な方向に延長されたアーム部を備え、アーム部の端部近傍の位置にコンタクト部を有する電極配線部を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】簡単な構成で、耐圧を保持しつつ小型化を図ることができる半導体装置を提供する。

【解決手段】ドレイン側拡散層112”Aにおけるチャネル領域116側の側面の少なくとも一部を除いた全面が、酸化膜107により、覆われている。酸化膜107は、拡散層112”Aとシリコン基板101との間の短絡を防止する。このため、酸化膜107の厚みを薄くしても、耐圧を確保できるので、装置の小型化を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】改良された縦型のMOSトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10の主面に対してほぼ垂直に延在するチャネル領域22と、チャネル領域22の下部に設けられた第1の拡散層領域22aと、チャネル領域の上部に設けられた第2の拡散層領域22bと、半導体基板10の主面に対してほぼ垂直に延在し、ゲート絶縁膜30を介してチャネル領域22の側面に設けられた第1のゲート電極34と、半導体基板10の主面とほぼ平行に延在し、第1のゲート電極34の上部に接続された第2のゲート電極35aと、第1の拡散層領域22aに接続され、第2のゲート電極と交差する埋め込み配線21を備えている。第2のゲート電極35aの平面的な位置は、第1のゲート電極34の平面的な位置に対してオフセットされている。

(もっと読む)

半導体装置および半導体装置を製造する方法

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびそれを製造する方法を提供する。

【解決手段】本発明の半導体装置は、素子分離領域と活性領域を有する半導体装置であって、活性領域とゲート酸化膜が接する第1の面より上に、ソース領域およびドレイン領域の一部が存在し、該ソース領域および/または該ドレイン領域と、該ソース領域および/または該ドレイン領域に電気的に接続される電極とが接する第2の面が、該第1の面に対して傾いている。

(もっと読む)

半導体装置

【課題】 トレンチ構造を有する横型半導体装置の駆動能力を向上させる。

【解決手段】 ウェルには、ゲート幅方向にウェルに凹凸を設けるためのトレンチ部が形成されており、絶縁膜を介して、トレンチ部の内部及び上面部にゲート電極が形成されている。ゲート電極のゲート長方向の一方の側にはソース領域が形成されており、他方の側にはドレイン領域が形成されている。ソース領域とドレイン領域は、何れも、トレンチ内部に充填された不純物を含む多結晶シリコンからの不純物拡散によって形成され、ゲート電極の底部近傍(トレンチ部の底部近傍)の深さまで形成されている。このように、ソース領域とドレイン領域を深く形成することで、ゲート電極部位で浅い部分に集中して流れていた電流がトレンチ部の全体に一様に流れるようになり、ウェルに形成された凹凸によって実効的なゲート幅が広がる。この結果、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

半導体装置の製造方法

【課題】 接合深さに起因する特性のバラツキを抑制可能な、極浅不純物拡散領域を有する半導体装置の製造方法を提供する。

【解決手段】 半導体基板面11にゲート酸化膜12、ゲート電極13、保護絶縁膜14を順次形成した後、不純物注入を行い、極浅不純物拡散領域18を形成後、極浅不純物拡散領域18上に、半導体基板11の不純物拡散係数以上の不純物拡散係数を有する半導体材料膜21を成膜する。その後、アニール処理を行って、前記極浅不純物拡散領域を活性化して極浅接合を形成する。

(もっと読む)

高耐圧半導体装置

【課題】オフ動作時における耐圧を低下させることなくオン動作時における素子抵抗を低減する。

【解決手段】p型半導体基板1の主表面上にはn-層2が形成される。このn-層2の表面にはp-拡散領域5が形成される。このp-拡散領域5の一方の端部に連なるようにp拡散領域6が形成される。p-拡散領域5内には、このp-拡散領域5よりも高濃度のp型の不純物を含むp拡散領域20が複数個形成される。p-拡散領域5と間隔をあけてp拡散領域3が形成される。このp拡散領域3とp-拡散領域5の間に位置するn-層2の表面上に酸化膜10を介在してゲート電極9が形成される。p拡散領域6の表面と接触してドレイン電極12が形成される。また、p拡散領域3と隣接してn拡散領域4が形成され、このn拡散領域4とp拡散領域3との双方の表面に接触してソース電極11が形成される。

(もっと読む)

高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタ

【課題】 マスク工程を簡略化しながらも、レイアウト面積を縮小した高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法を提供することを目的とする。

【解決手段】 基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の一方の側に位置する基板の内部に形成されたドレイン領域と、ゲート電極の他方の側に位置する基板の内部に形成されたソース領域と、ドレイン領域上に形成され、且つ不純物拡散領域を介してドレイン領域と電気的に接続された堆積型ドレイン層と、ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、ゲート電極の前記ドレイン側の側壁に形成され、堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有する。

(もっと読む)

高耐圧半導体装置

【課題】オフ動作時における耐圧を低下させることなくオン動作時における素子抵抗を低減する。

【解決手段】p型半導体基板1の主表面上にはn-層2が形成される。このn-層2の表面にはp-拡散領域5が形成される。このp-拡散領域5の一方の端部に連なるようにp拡散領域6が形成される。p-拡散領域5内には、このp-拡散領域5よりも高濃度のp型の不純物を含むp拡散領域20が複数個形成される。p-拡散領域5と間隔をあけてp拡散領域3が形成される。このp拡散領域3とp-拡散領域5の間に位置するn-層2の表面上に酸化膜10を介在してゲート電極9が形成される。p拡散領域6の表面と接触してドレイン電極12が形成される。また、p拡散領域3と隣接してn拡散領域4が形成され、このn拡散領域4とp拡散領域3との双方の表面に接触してソース電極11が形成される。

(もっと読む)

高耐圧半導体装置

【課題】オフ動作時における耐圧を低下させることなくオン動作時における素子抵抗を低減する。

【解決手段】p型半導体基板1の主表面上にはn-層2が形成される。このn-層2の表面にはp-拡散領域5が形成される。このp-拡散領域5の一方の端部に連なるようにp拡散領域6が形成される。p-拡散領域5内には、このp-拡散領域5よりも高濃度のp型の不純物を含むp拡散領域20が複数個形成される。p-拡散領域5と間隔をあけてp拡散領域3が形成される。このp拡散領域3とp-拡散領域5の間に位置するn-層2の表面上に酸化膜10を介在してゲート電極9が形成される。p拡散領域6の表面と接触してドレイン電極12が形成される。また、p拡散領域3と隣接してn拡散領域4が形成され、このn拡散領域4とp拡散領域3との双方の表面に接触してソース電極11が形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】チャネル領域に応力を印加しつつ、シリサイド層を膜状に形成するとともに、シリサイド層の異常成長が抑制された半導体装置の製造方法および半導体装置を提供する。

【解決手段】まず、第1工程では、シリコン基板11上にゲート絶縁膜12を介してゲート電極13を形成する。次に、第2工程では、ゲート電極13をマスクにしたエッチングにより、シリコン基板11の表面層を掘り下げる。次いで、第3工程では、掘り下げられたシリコン基板11の表面に、SiGe層からなる第1の層21をエピタキシャル成長させる。続いて、第4工程では、第1の層21上に、第1の層21よりもGe濃度の低いSiGe層またはSi層からなる第2の層22を形成する。その後の第5工程では、第2の層22の少なくとも表面側をシリサイド化して、シリサイド層Sを形成する。

(もっと読む)

固体撮像素子及びその製造方法、並びに半導体装置及びその製造方法

【課題】p型不純物領域の活性化を低温で行うことを可能にする固体撮像素子の製造方法を提供する。

【解決手段】光電変換が行われる受光センサ部が半導体基体内に形成され、この半導体基体の表面側に配線層又は電極層が形成され、半導体基体に、表面側とは反対の裏面側から光を入射させる裏面照射型構造を有する固体撮像素子を製造する際に、半導体基体の裏面側の部分をアモルファス化してアモルファス半導体層62を形成する工程と、半導体基体の裏面側へp型不純物をイオン注入63する工程とを、それぞれ行い、その後に、レーザーアニール65によってp型不純物を活性化させることにより、半導体基体の裏面側にp型半導体領域31を形成する。

(もっと読む)

1 - 20 / 39

[ Back to top ]