Fターム[5F140BH31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | SD近傍領域(SD領域と導電型は除く) (1,891)

Fターム[5F140BH31]の下位に属するFターム

形状、配置 (996)

不純物分布 (48)

基板(ウェル)コンタクト領域 (573)

n、p型以外の領域(絶縁膜、i層など) (264)

Fターム[5F140BH31]に分類される特許

1 - 10 / 10

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

スイッチング素子及びこれを用いた電源装置

【課題】ソース電極とドレイン電極間の容量を低減し、スイッチングロスを減らすことができるスイッチング素子、及び該スイッチング素子を搭載した効率が向上した電源装置の提供。

【解決手段】Si基板1と、該Si基板1上に形成されたソース電極8及びドレイン電極9を有してなり、ソース電極8及びドレイン電極9の配置方向と直交する方向の層中であって、ソース電極8及びドレイン電極9のいずれか一方のみと接している領域に、p型領域とn型領域が接している部分24であるpn接合を少なくとも1つ有するスイッチング素子である。

(もっと読む)

半導体デバイスのための非対称スペーサ構造体を形成する方法

【課題】 デバイスのゲートとソースとの間の低い直列抵抗を維持し、同時に、ゲートからドレインへの過剰なオーバーラップによって形成される悪影響を最小限にするFETデバイスの製造を可能にする。

【解決手段】半導体基板の上に少なくとも1対の隣接して離間配置された、オフセット・スペーサ114を備えるゲート構造体102の上にスペーサ層132を形成するステップであって、ゲート構造体は、スペーサ層がゲート構造体間の領域で第1の厚さで形成され、その他の場所で第2の厚さで形成されるように離間配置され、第2の厚さは第1の厚さより厚い、ステップと、1対の隣接して離間配置されたゲート構造体のオフセット・スペーサに隣接して非対称スペーサ構造体124a、bを形成するようにスペーサ層をエッチングするステップとを含み、非対称スペーサ構造体は、ソース及びドレイン領域の画定において用いられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTのESD耐性を高くしつつ、IGBTのバイポーラトランジスタを確実に動作させる。

【解決手段】シンカー層115は第1導電型ウェル102に接しており、かつ第1導電型コレクタ層108及び第2導電型ドリフト層104から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

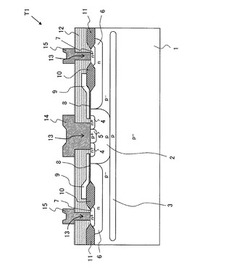

半導体装置及びその製造方法

基板(11)上に形成されたフィン型半導体領域(13)の両側部にエクステンション領域(17)が設けられている。フィン型半導体領域(13)を跨ぐと共にエクステンション領域(17)と隣り合うようにゲート電極(15)が形成されている。ゲート電極(15)と隣り合う領域のフィン型半導体領域(13)の上部に、エクステンション領域(17)よりも高い抵抗率を有する抵抗領域(37)が形成されている。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

ダイレクトトレンチポリシリコンコンタクトを備える横型トレンチMOSFETおよびその形成方法

横型トレンチMOSFETは、装置セグメントとゲートバスセグメントとを含むトレンチを備える。トレンチのゲートバスセグメントは、基板を覆って存在する誘電体層に形成される導電性プラグによってコンタクトされ、これにより従来の表面ポリシリコンブリッジ層が不要となる。導電性プラグは、誘電体層にある実質的に垂直な穴に形成される。ゲートバスセグメントは、トレンチの装置セグメントよりも幅が広くてもよい。この方法は、トレンチ中の導電性材料がエッチングされる間にシャロートレンチアイソレーション(STI)を形成するステップを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】好適な特性を有するゲート絶縁膜及びゲート電極からなるP型FET及びN型FETを備える半導体装置を提供する。

【解決手段】P型FET形成予定領域とN型FET形成予定領域とにわたって、基板上にゲート絶縁膜を形成し、ゲート絶縁膜上にP型FET用のゲート電極層を形成し、P型FET形成予定領域とN型FET形成予定領域とにおいて、P型FET用のゲート電極層を加工することにより、P型FET形成予定領域にP型FET用のゲート電極を形成すると共に、N型FET形成予定領域にダミーゲート電極を形成し、N型FET形成予定領域において、ゲート絶縁膜上からダミーゲート電極を除去することにより、溝を形成し、溝にゲート電極材料を埋め込むことにより、ゲート絶縁膜上にN型FET用のゲート電極を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体製造装置及び半導体装置の製造方法

【課題】半導体装置の特性ばらつきを抑えることが可能な半導体装置の製造方法及び半導体製造装置を提供する。

【解決手段】半導体ウェハ上にトランジスタ電極を形成する工程と、前記トランジスタ電極の加工形状を測定する工程と、測定された前記加工形状に基づき、不純物導入領域を予測する工程と、前記予測された不純物導入領域に対して、設計基準特性を得るための不純物導入条件を算出する工程と、前記算出された不純物導入条件で、前記半導体ウェハに不純物を導入する工程を備える。

(もっと読む)

半導体素子

【課題】 基板のフェルミ準位の影響を低減することができる半導体素子を提供する。

【解決手段】 半導体基板1の一方の面上に、この半導体基板1と同じ半導体材料を使用しドーパントの種類又は濃度を変えて緩衝層2を形成する。そして、緩衝層2上に夫々局所的に半導体層3a及び3bを形成し、この半導体層3a及び3bの対向する端部上及びこれらの間に、半導体基板1と同じ半導体材料を使用し、半導体層3a及び3bよりもドーパント濃度が低いチャネル層4を形成する。その際、緩衝層2の厚さD(nm)を、半導体基板1のフェルミ準位とチャネル層4のフェルミ準位との差V(eV)、半導体基板1の有効ドナーの濃度又は有効アクセプタの濃度NS(m−3)、緩衝層2の有効ドナーの濃度又は有効アクセプタの濃度NB(m−3)、チャネル長L(m)、素電荷e、緩衝層2の比誘電率εB、真空の誘電率をε0から求められる下記数式の範囲内とする。 (もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]