Fターム[5F140BH45]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | SD近傍領域(SD領域と導電型は除く) (1,891) | n、p型以外の領域(絶縁膜、i層など) (264)

Fターム[5F140BH45]に分類される特許

1 - 20 / 264

半導体装置

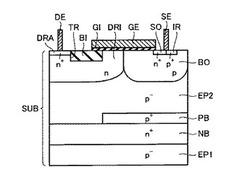

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】良好な特性の確保、素子サイズの増加の回避、及び製造プロセスの簡素化を実現できる半導体装置の製造方法を提供する。

【解決手段】Si基板111の主面に、LOCOS酸化膜112bを含む酸化膜112を形成する工程と、Si基板111の主面の側に、ソース・ゲート形成領域113aとドレイン形成領域113bとを形成する工程と、レジスト116をマスクとして、Si基板111の主面の側のLOCOS酸化膜112bで覆われていないトレンチ114を通してイオン117注入を行い、イオン注入層118を形成する工程と、LOCOS酸化膜112b上及びソース・ゲート形成領域113a上を部分的に覆うようにゲート電極119を形成する工程とを有し、イオン注入層118のゲート電極119側の端部とゲート電極119のイオン注入層118側の端部との間に間隔121が存在するように、各工程を行う。

(もっと読む)

半導体装置

【課題】素子面積を増加させることなく、高耐圧の半導体装置を実現させる。

【解決手段】第1方向に沿ったソース領域、ゲート電極を挟んでソース領域とは反対側に第1方向に沿ったドレイン領域、一部がゲート電極下面と対向しソース領域とドレイン領域との間に設けた絶縁体層、一部がゲート電極下面と対向し絶縁体層よりもソース領域側に設けたベース領域、一部が第2方向に第2長さを有してゲート電極下面と対向し、ベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子活性領域部、ゲート絶縁膜の上に設けたゲート電極、ソース領域、一部がゲート電極下面と対向して設けた絶縁体層、一部がゲート電極下面と対向して絶縁体層よりもソース領域側に設けたベース領域、一部が第1方向に第2長さよりも短い第1の長さを有してゲート電極下面と対向してベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子終端領域部と、を備える。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置

【課題】長期に亘って信頼性の高い横型MISFETを有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板11上に形成された半導体層13と、半導体層13に溝状に形成され、その内壁が絶縁膜31で被覆され、絶縁膜31の内部にゲート電極32が埋設されたトレンチ溝30と、半導体層13上に、トレンチ溝30と少なくとも一部が対向配置する位置に形成されたゲート配線51と、ゲート配線51を挟むように半導体層13上に形成されたソース電極52、及びドレイン電極53とを具備する。半導体層13におけるオン動作時の電流経路は、ソース電極52とドレイン電極53の間の半導体層13の表面領域を実質的に経由せず、上記トレンチ溝30の側面近傍を経由する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、上面にトレンチが形成された半導体基板と、前記トレンチ内に設けられた絶縁部材と、を備える。そして、前記半導体基板と前記絶縁部材との間には、空隙が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル層を具備する半導体構造の改良を図ること。

【解決手段】 実施形態の半導体構造は、第1の格子定数を具備する第1の結晶を具備する半導体基板と、前記半導体基板上に形成され、第2の格子定数を具備する第2の結晶を具備する多層エピタキシャル層とを具備している。前記第1の格子定数は、前記第2の格子定数と異なる。前記多層エピタキシャル層は、第1のエピタキシャル層および第2のエピタキシャル層を具備している。前記第1のエピタキシャル層の第1の導電型不純物は、前記第2のエピタキシャル層の第2の導電型不純物よりも少ない。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、パワー半導体素子を提供する。

【解決手段】半導体基材内に第1の伝導型のドリフト領域2と、半導体基材内にドリフト領域2に隣接して配置され半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3の間に配置された蓄積誘電体4と、基材領域8と、基材領域8から分離され蓄積誘電体4に隣接するドレイン領域5と、基材領域8によりドリフト領域2から分離されるソース領域9と、ゲート誘電体16により半導体基材から絶縁されソース領域9からドリフト領域2に到るまで基材領域8に隣接して伸びたゲート電極15と、ドレイン領域5と接したドレイン電極11と、ドレイン領域5と相補的にドープされた半導体領域27とを含み、半導体領域27はドレイン電極11とドリフト領域2の間に配置されドレイン電極11に隣接する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】LDMOSトランジスタのオン耐圧を改善する。

【解決手段】フィールドドレイン絶縁部120は、第1絶縁膜126及び高誘電率絶縁膜124を有している。第1絶縁膜126は、平面視で少なくともフィールドドレイン絶縁部120の中央部に位置している。高誘電率絶縁膜124は、フィールドドレイン絶縁部120の底面の縁のうち少なくともドレイン領域142に近接する部分に位置しており、第1絶縁膜126よりも誘電率が高い。また高誘電率絶縁膜124は、平面視でフィールドドレイン絶縁部120の中央部には位置していない。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置及びその製造方法

【課題】特性バラツキを低減することができるような半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、ゲート絶縁膜を介して基板の表面を第1導電型チャネル領域から酸化膜の一部までを覆い、且つ、第1導電型チャネル領域と酸化膜との間に開口部を有するゲート電極と、この開口部下の基板に形成された第2導電型ドリフト領域の第2の部分とを有する。

(もっと読む)

1 - 20 / 264

[ Back to top ]