Fターム[5F140BH32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | SD近傍領域(SD領域と導電型は除く) (1,891) | 形状、配置 (996)

Fターム[5F140BH32]の下位に属するFターム

領域−全体 (124)

領域−下部 (108)

領域−上部 (181)

領域−角部 (136)

領域5(接触) (30)

領域6(非接触) (60)

領域7(離間) (53)

SD領域中に形成されているもの (263)

Fターム[5F140BH32]に分類される特許

1 - 20 / 41

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

半導体装置

【課題】Si混晶層における選択成長用マスクの開口率の違いによりエピタキシャル成長が不均一となることを防止すると共に、半導体素子のキャリア移動度を向上できるようにする。

【解決手段】半導体装置は、半導体基板100の上部に形成された素子分離膜101と、素子分離膜に囲まれてなる素子活性領域102と、該素子活性領域102に形成され正孔をキャリアとするチャンネル領域100aとを有するP型MIS−FET200Pと、素子分離膜における素子活性領域102の周辺部に形成された複数のダミー活性領域105とを備えている。複数のダミー活性領域105のうち、正孔の移動方向と対向する位置に形成されたダミー活性領域のみをシリコンとゲルマニウムとを含むSiGe付きダミー活性領域106としている。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

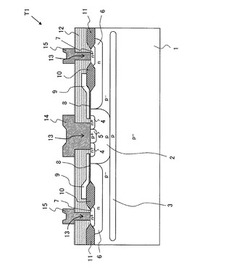

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動電流が大きくリーク電流の少ない低消費電力のMISトランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】チャネル領域を有する半導体基板と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、半導体基板内にチャネル領域を挟むように配置されたソース拡散層及びドレイン拡散層と、ソース拡散層側の半導体基板内に形成された第1のポケット不純物層と、ドレイン拡散層側の半導体基板内に形成された第2のポケット不純物層とを有し、第1のポケット不純物層は、ソース拡散層のエクステンション不純物層の濃度ピーク位置よりも深い位置に濃度ピークを有しており、第2のポケット不純物層は、ドレイン拡散層のエクステンション不純物層の濃度ピーク位置よりも浅い位置に濃度ピークを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】より高温の活性化FLAを行ってもウェハが割れることなく、SDエクステンション抵抗を下げることができる半導体装置の製造方法を提供する。

【解決手段】ウェハをウェハ表面温度1100℃以上に0.1〜10ミリ秒で加熱するための高強度のフラッシュランプアニールを照射する際、その直前のウェハ表面温度を800〜1000℃と高温にする。ウェハの予備加熱を、波形を調整したフラッシュで行うことにより不純物の拡散を抑制する。この手法により、アモルファス層を形成していないウェハ表面を効果的に活性化できるため、欠陥が少なく、かつ浅く低抵抗な接合が形成できる。

(もっと読む)

半導体装置

【課題】ゲート幅方向端部Eを取り囲むフィールド酸化膜コーナー部19近傍の活性領域14に形成された、高濃度N型ドリフト層5の部分で絶縁破壊することにより、DMOSトランジスタのソース・ドレイン間絶縁破壊電圧BVDSが低下することを防止する。

【解決手段】ゲート幅方向端部Eの活性領域14の幅を、ゲート幅方向中央部より広く形成することによりフィールド酸化膜コーナー部19を、ゲート幅方向端部Eに形成されたP型ボディ層4からゲート幅方向端部の外側に遠ざける。これにより、デバイス面積を拡大することなく、P型ボディ層4から、フィールド酸化膜コーナー部19の近傍に形成される高濃度N型ドリフト層5を遠ざける事ができる。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタが形成される半導体層の任意の位置にパンチスルーを抑制するための高濃度層を形成する。

【解決手段】半導体装置の製造方法は、第1導電型の半導体基板11上にマスク層13を形成する工程と、半導体基板11をマスク層13をマスクとしてエッチングし、半導体基板11に凸状半導体層14を形成する工程と、半導体基板11上で凸状半導体層14の下部を覆うように第1絶縁層15を形成する工程と、第1絶縁層15に第1導電型の不純物を導入し、凸状半導体層14の下部に高濃度層16を形成する工程と、第1絶縁層15の表面上で凸状半導体層14の側面上にゲート絶縁膜17を形成する工程と、ゲート絶縁膜17上にゲート電極18を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】高耐圧と速い動作とを共に実現することが可能な半導体装置を提供する。

【解決手段】N型基板1上のN型の半導体層2、半導体層2の表面の、P型の第1拡散層4及び、この第1拡散層4と互いに離間し、かつ、第1拡散層4を囲む、P型の第2拡散層4から成る第1ソース領域及び第1ドレイン領域、第1拡散層4の表面のP型の第3拡散層5、第2拡散層4の表面のP型の第4拡散層7、第2拡散層4の表面と半導体層2の表面とをまたぎ、第4拡散層7と電気的に接続された、N型の第5拡散層8、第1ソース領域及び第1ドレイン領域及び半導体層2上の第1ゲート電極10、第1ゲート電極10と容量接続されているドレイン電極13、ドレイン電極13と第3拡散層5とを電気的に接続する配線12,15を含む、半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、薬液処理やエッチング工程の影響を受けず、設計通りの耐圧特性を得ることができる半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】周囲が素子分離領域70で囲まれたアクティブエリア80を有し、該アクティブエリア上にゲート10が延在し、該ゲートと前記素子分離領域とで周囲が囲まれて前記アクティブエリアが露出したアクティブエリア露出部85を有する半導体装置150であって、

該ゲートの隣に略平行に延在して配置され、前記アクティブエリア露出部に形成されたソース30と、

該ソースを側方及び下方から覆い、前記アクティブエリア露出部を包含して前記ゲート及び前記素子分離領域に到達するように形成されたボディ層50と、

該ソースの延在方向の延長上にある前記ボディ層の外側に、前記ボディ層を側方及び下方から覆うように形成された前記ボディ層と同じ導電型の追加不純物層60と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】ハンプ特性の発生を抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、一導電型の半導体基板表面に設けられた素子分離膜12、一対の端部が素子分離膜12と素子形成領域13との境界上に位置するゲート電極14、ゲート電極14の直下の領域を挟んで配置される逆導電型のソース領域15、ドレイン領域16、素子形成領域13内に形成された一導電型の不純物拡散領域17を備える。ソース領域15は、素子形成領域13内のゲート電極14の直下の領域のうち、素子分離膜12と素子形成領域13との境界側の領域141に対し離間している。不純物拡散領域17は、境界側の領域141と隣接する部分が、ソース領域15と、素子分離膜12との間に配置されるとともに、ソース領域15と、境界側の領域141とに接する。不純物拡散領域17は、ドレイン領域16と素子分離膜12との間には配置されていない。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のソフトエラーの発生を抑制する技術を提供する。

【解決手段】半導体集積回路装置を構成するMISFET(2)を以下のように構成する。そのMISFET(2)は、第一導電型のドレイン拡散層(4)とソース拡散層(3)、およびゲート電極(5)、第一導電型と反対導電型の第二導電型の基板(8)/ウエル(9)から構成される。そして、そのMISFET(2)において、ドレイン拡散層(4)の周囲少なくとも2辺の素子分離面に対向する位置に、第一導電型と同導電型の第一の拡散層(11)(12)を、素子分離絶縁膜(6)を介して所定間隔で2箇所以上設け、ソース拡散層近傍またはソース拡散層に接触するように、第二導電型の第二の拡散層(16)を設ける。

(もっと読む)

1 - 20 / 41

[ Back to top ]