Fターム[5F140BH33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | SD近傍領域(SD領域と導電型は除く) (1,891) | 形状、配置 (996) | 領域−全体 (124)

Fターム[5F140BH33]に分類される特許

1 - 20 / 124

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】安定に動作する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、基板11内に形成された第1導電型のウェル13と、ウェル13上にゲート絶縁膜17を介して配置されるゲート電極18と、ゲート電極18を挟んで基板11内に対向して配置される第2導電型のソース領域15及びドレイン領域16と、基板11内にソース領域15と隣接して配置され、ウェル1に電気的に接続される第1導電型のウェルタップ19と、ウェル13とウェルタップ19とに接し、ウェル13よりも不純物濃度が高く、第1導電型を有するポケット領域20と、を備える。

(もっと読む)

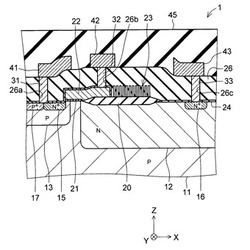

高耐圧半導体装置

【課題】容量素子の直列接続を形成するフィールドプレートにおいて、導電性薄膜の間の層間絶縁膜の厚さを増加させても、容量素子による電圧の分圧を均一にできる高耐圧半導体装置を提供する。

【解決手段】本発明の高圧半導体装置は、第1導電型の第1半導体領域と、第1半導体領域と隣接して形成された第2導電型の第2半導体領域と、第2の半導体領域とで第1導電型の第1半導体領域を挟んで形成された、第1導電型の第3半導体領域と、第1半導体領域上に形成された第1絶縁膜上に所定の周期で配列された第1導電膜と、第1導電膜上に形成された第2絶縁膜に、平面視で第1導電膜の離間領域と重なり、かつ当該離間領域の両側に配置されている第1導電膜と一部が重なる位置に周期的に配置されている第2導電膜とを備え、第2導電膜は、第1導電膜の離間領域と対向する領域に第1凸部が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】新規なDTMOSトランジスタの製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1領域と、第1領域に接続しこれより幅狭の第2領域と、第2領域に接続しこれより幅狭の第3領域とを含む半導体領域の画定工程、半導体領域に第1導電型不純物でウェル領域を形成する工程、ウェル領域上へのゲート絶縁膜形成工程、第3領域を幅方向に横断する第1部と、第1部から第1領域上に延びた第2部とを含むゲート電極を形成する工程、ゲート電極側面に、第2領域の一部を覆い他の一部を露出させるサイドウォールを形成する工程、第1領域及び第2領域の他の一部にゲート電極及びサイドウォールをマスクとし第2導電型不純物を注入する工程、熱処理による第2導電型不純物拡散工程、サイドウォールの一部を薬液で除去する工程、第1領域及び第2領域の他の一部へのシリサイド層形成工程を有する。

(もっと読む)

半導体装置およびその製造方法、固体撮像素子、電子情報機器

【課題】従来のようにトランジスタゲート面積を大きくすることなく、より簡単な製造工程で、トランジスタのソース側ゲート端のイオン注入ダメージにより発生するソース側ゲート端付近の欠陥を低減することにより、ランダムノイズを効果的に低減する。

【解決手段】ドレイン側のLDD領域のN型拡散層11だけがゲート電極6の他方端の下に潜り込んで、ドレイン側のLDD領域のN型拡散層11がゲート電極6と平面視でオーバラップし、ソース側のLDD領域のN型拡散層12はゲート電極6の一方端の下に潜り込まず、ソース側のLDD領域のN型拡散層12がゲート電極6と平面視でオーバラップしておらず、ソース側のLDD領域のN型拡散層12がゲート電極6の一方端と離間して形成されている。

(もっと読む)

半導体装置

【課題】移動体通信装置用半導体装置(RFパワーモジュール)の電力付加効率を向上させる。

【解決手段】パワーMOSFETのゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に最も近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くする。これにより、オン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅素子をシリコンパワーMOSFETで構成したRFパワーモジュールの小型化と電力付加効率の向上を図ることができる。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセスばらつきの影響が小さい半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板の上層部分に設けられた第1導電形領域と、前記第1導電形領域の上層部分に相互に離隔して配置された第2導電形のソース領域及びドレイン領域と、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、を備える。そして、前記第1導電形領域のうち前記ゲート電極の直下域に相当するチャネル領域における実効的な不純物濃度は、前記ゲート絶縁膜との界面において最も高く、下方に向かうにつれて減少している。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

1 - 20 / 124

[ Back to top ]