Fターム[5F140BH34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | SD近傍領域(SD領域と導電型は除く) (1,891) | 形状、配置 (996) | 領域−下部 (108)

Fターム[5F140BH34]に分類される特許

1 - 20 / 108

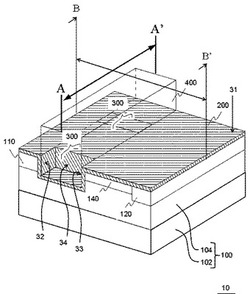

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置

【課題】トンネルトランジスタの高電圧での駆動力を向上させることが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層を備える。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】 ファセット起因による短チャネル効果を回避すること。

【解決手段】 半導体基板(1)に設けられたMISトランジスタ(4,5,13)からなる半導体デバイス(200)は、半導体基板(1)に設けられた素子分離領域(2)と、素子分離領域(2)によって区画された活性領域(3)と、活性領域(3)に設けられたMISトランジスタのチャネル領域よりも上方へ突出したMISトランジスタのソース/ドレイン領域(13)と、ソース/ドレイン領域(13)の下方に設けられた拡散層(12)と、を備える。ソース/ドレイン領域(13)の導電型に対する拡散層(12)の導電型が逆の極性となっている。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11上に、ダミーゲート電極及びダミーコンタクトプラグの側面を覆う層間絶縁膜16を形成後、ダミーゲート電極、ダミーコンタクトプラグを選択的に除去して、ゲート電極形成用溝17及びコンタクト孔18を同時に形成し、次いで、ゲート電極形成用溝17内、コンタクト孔18内、及び層間絶縁膜16の上面を覆う高誘電率絶縁膜42を成膜し、次いで、斜めイオン注入法により、ゲート電極形成用溝17の下部17Aに形成された高誘電率絶縁膜42にイオン注入しないように、高誘電率絶縁膜42を介して、半導体基板に不純物拡散領域15を形成し、次いで、イオン注入された高誘電率絶縁膜42を選択的に除去することで、ゲート電極形成用溝の下部にゲート絶縁膜を形成し、かつコンタクト孔から不純物拡散領域15の上面を露出させる。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体デバイスおよび方法

半導体装置の製造方法

【課題】不純物イオン注入時に形成されたフレンケル型結晶欠陥を終端させ、ボロンの増速拡散を抑制することで、逆短チャンネル効果を改善した半導体装置の製造方法を提供する。

【解決手段】MOS型トランジスタを備えた半導体装置の製造方法において、MOSトランジスタは、P型ウェル領域と、N型ソース・ドレイン領域と、チャネル領域と、ゲート電極と、からなるNMOSトランジスタであって、N型ソース・ドレイン領域を不純物イオン注入により形成する工程と、ソース・ドレイン領域と同一領域に、ハロゲン元素をイオン注入する工程と、ソース・ドレイン領域を活性化させるための活性化熱処理工程とを含む。

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

自己整合損傷層を有するデバイス構造体の形成方法

【解決課題】 自己整合損傷層を有するデバイス構造体の形成方法を提供すること。

【解決手段】デバイス構造体は、基板の半導体材料内部に画定された第1導電型の第1及び第2ドープ領域を有する。逆の導電型の第3ドープ領域が、横方向に第1ドープ領域を第2ドープ領域から分離する。ゲート構造部が基板の上表面に配置され、第3ドープ領域と垂直方向で重なる関係を有する。第1結晶損傷層は基板の半導体材料の内部に画定される。第1結晶損傷層は、基板の半導体材料によって取り囲まれた第1の複数のボイドを有する。第1ドープ領域は、第1結晶損傷層と基板の上表面との垂直方向の間に配置される。第1結晶損傷層は横方向に第3ドープ領域内には延びない。

(もっと読む)

1 - 20 / 108

[ Back to top ]