Fターム[5F140BJ05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 最下層材料 (3,069) | 金属 (2,883)

Fターム[5F140BJ05]の下位に属するFターム

合金 (116)

高融点金属 (492)

金属シリサイド (1,738)

金属化合物(窒化物、酸化物) (134)

Fターム[5F140BJ05]に分類される特許

201 - 220 / 403

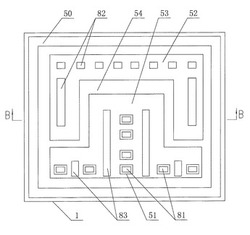

定電流源部品及び製造手段

【課題】直接に交流電源及び直流電源に応用でき、過流過電圧保護機能がある定電流源部品を提供する。

【解決手段】当該部品には、シリコン基板1、于シリコン基板1正面に形成した酸化層、酸化層正面に所在するドレイン金属、ソース金属、グリッド金属、シリコン基板1に植え込んだP+保護リング50、N+ドレイン領域52、N+ソース領域53、N+ソース領域53に所在するP+下敷領域51、N+ドレイン領域52とN+ソース領域53の間を接続するN−通路領域54を有して、ドレイン金属、ソース金属がそれぞれN+ドレイン領域52、N+ソース領域53、P+下敷領域51に接続して、ソース金属、グリッド金属が接続金属で接続する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体素子ならびに半導体素子製造法

【課題】炭化珪素を基板とする半導体素子において、基板の欠陥密度に関わらず、炭化珪素エピタキシャル層の非極性面上において、電極/炭化珪素界面、あるいは酸化膜(絶縁膜)/炭化珪素界面の電気的特性と安定性を向上させる手段を提供する。

【解決手段】炭化珪素からなる半導体基板と、前記半導体基板上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるゲート電極とを有する半導体素子。前記半導体基板表面の前記ゲート絶縁膜との接合面は、巨視的には非極性面に平行であり、かつ微視的には非極性面と極性面からなり、前記極性面ではSi面またはC面のいずれか一方の面が優勢である。炭化珪素からなる半導体基板と、前記半導体基板上に形成される電極とを有する半導体素子。前記半導体基板表面の前記電極との接合面は、巨視的には非極性面に平行であり、かつ微視的には非極性面と極性面からなり、前記極性面ではSi面またはC面のいずれか一方の面が優勢である。

(もっと読む)

半導体装置の製造方法

【課題】TaCをSiCのエッチングを行なうためのマスクの素材として採用可能とすることにより、製造工程を簡略化することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置であるMOSFETの製造方法は、SiC部材であるn型SiC層を準備する基板準備工程およびn型SiC層形成工程と、n型SiC層上にTaC膜を形成するTaC膜形成工程と、TaC膜をマスク形状に成形するTaCマスク形成工程と、マスク形状に成形されたTaC膜をマスクとして用いて、n型SiC層をエッチングするn型SiC層エッチング工程とを備えている。そして、n型SiCz層エッチング工程では、Fを含有するガスとOを含有するガスとを含む混合ガスを用いたドライエッチングによりn型SiC層がエッチングされる。

(もっと読む)

CMOS素子及びその製造方法

【課題】CMOS素子及びその製造方法を提供する。

【解決手段】基板上に形成されたエピ層と、エピ層のそれぞれ異なる領域上に形成された第1及び第2半導体層と、第1及び第2半導体層上にそれぞれ形成されたPMOS及びNMOSトランジスタと、を備えるCMOS素子である。

(もっと読む)

半導体装置

【課題】アップドレイン構造のMOSFETでは、ドレイン電極直下に設けた電流の引き上げ領域に電流が集中するため、電流経路の抵抗値の低減には限界があった。

【解決手段】素子領域としては無効領域となるゲートパッド下方の一部に高濃度のn型不純物領域を配置する。これにより、素子領域を狭めることなくまたチップを拡大することなく、ドレイン抵抗の低減が可能となる。また、n型不純物領域とドレイン電極をチップ外周端に設けることにより、従来のアニュラー領域やシールドメタルを別途も受けなくても、基板の空乏層を終端させることが可能となる。つまり、n型不純物領域とドレイン電極によりアニュラー領域やシールドメタルを兼用できるので、必要な構成を備えたアップドレイン構造のMOSFETでありながら、素子領域の縮小やチップ面積の増大を回避できる。

(もっと読む)

半導体装置

【課題】MOSトランジスタを有する半導体装置であって、エリアパッド下のMOSトランジスタの特性変動を抑制することが可能な半導体装置を提供する。

【解決手段】MOSトランジスタとエリアパッドを有する半導体装置10であって、結晶方位面<110>を表面とするシリコンを材料とする半導体チップ11と、ソース領域、ゲート領域及びドレイン領域がシリコンの結晶方位<110>の方向に並び、半導体チップ11内に形成される複数のMOSトランジスタ12と、半導体チップ11上のエリアパッドとして2次元状に形成された複数の接合用電極パッド13と、複数の接合用電極パッド13それぞれの上に形成された接合用バンプ14とを備え、複数の接合用電極パッド13は、その中心点が結晶方位<110>の方向に対して斜めの方向に並ぶことを特徴とする。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】オン抵抗を増大させることなく、高耐圧化を実現可能な半導体装置を提供する。

【解決手段】LDMOSトランジスタ1は、P型半導体基板13上に形成されたN型拡散領域2と、N型拡散領域2の表層に形成されたP型ボディ領域6と、P型ボディ領域6に形成されたN型ソース領域8と、N型ソース領域8と離間してN型拡散領域2の表層に形成されたN型ドレイン領域10と、N型拡散領域2上の、N型ソース領域8とN型ドレイン領域10との間の位置に、ゲート絶縁膜を介して形成されたゲート電極11と、N型拡散領域2内において、P型ボディ領域6の下方に、P型ボディ領域6と離間して形成されたP型拡散領域4とを備えており、P型ボディー領域6とP型拡散領域4との間に形成される空乏層容量によって電界の集中を緩和し、耐圧を向上させることが可能となる。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】高電圧動作するGaNベースの高出力化合物半導体装置を提供する

【解決手段】化合物半導体装置は、ソース領域およびドレイン領域の間にチャネル領域を含むIII−V族窒化物半導体層と、前記III−V族窒化物半導体層上に、前記チャネル領域を覆って形成された、金属酸化物成分を含む第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、前記チャネル領域において前記ゲート絶縁膜を露出する開口部を有する第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に、前記第2のゲート絶縁膜の表面を覆って形成され、前記開口部において前記第1のゲート絶縁膜に接するゲート電極と、前記III−V族窒化物半導体層上、前記ソース領域およびドレイン領域にそれぞれオーミック接触して形成されたソースおよびドレイン電極と、よりなる。

(もっと読む)

スピンFET及び磁気抵抗効果素子

【課題】素子抵抗の低抵抗化とMR比の向上とを同時に実現する。

【解決手段】本発明の例に係るスピンFETは、ソース・ドレイン部に、少なくとも半導体基板11/トンネルバリア12/低仕事関数材料13/強磁性体14からなる積層構造を有し、低仕事関数材料13は、未酸化のMg,K,Ca,Scのうちの1つ、又は、その1つを原子数比で50%以上含む合金から構成される。

(もっと読む)

高耐圧半導体装置

【課題】 高耐圧半導体装置では、高電圧配線に高電圧が印加された時、トランジスタのチャネル領域等が反転し、動作に異常をきたすことがあった。

【解決手段】高電圧配線32に高電圧が印加されたときに、意図的に反転する領域33を設け、高電圧が印加されているときにオン状態となる能動素子50を備える。すなわち、能動素子50は、ソース領域25およびドレイン領域26と、ソース領域25およびドレイン領域26に接続された低電圧配線28、29とを含む。高電圧配線32は、低電圧配線28、29と上下方向に重ならないように、かつ、ソース領域25およびドレイン領域26間の上を覆うように設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板上にオーミック電極を形成する際に、金属と炭化珪素との合金化熱処理を不要にする。

【解決手段】六方晶単結晶の炭化珪素基板11の(0001)面にリン(P)をイオン注入することで、その部分をアモルファス層12にする。次に、熱処理することで、アモルファス層12を立方晶単結晶のn型炭化珪素13に再結晶化させる。次に、そのn型炭化珪素13の上面にニッケル(Ni)を蒸着することで、電極14を形成する。炭化珪素13と電極14との間に形成されるショットキー障壁の高さが低くなり、合金化熱処理を用いることなく、電極14と炭化珪素13との間にオーミックコンタクトが実現される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に於いて、MIS界面特性を劣化させないゲート絶縁膜のPDA手法(熱処理方法)を提供する。

【解決手段】炭化珪素半導体基板2上に、熱酸化法により、0.5nm〜2nmの範囲内の厚みを有する酸化珪素5を形成する。更に、酸化珪素5の上に堆積法によって酸化膜6を形成して、ゲート絶縁膜としての積層酸化膜7を得る。その上で、酸化膜6の堆積温度よりも高温で、且つ、酸素濃度が0.05Pa以上で5Pa以下の範囲内に制御された減圧の酸素雰囲気下で、積層酸化膜7に対して熱処理を行うことで、ゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 チャネル抵抗の上昇を最小限に抑えつつ、トランジスタのコンダクタンス特性に優れた半導体装置を提供する。

【解決手段】 半導体基板上にMOS型トランジスタが形成してある半導体装置において、MOS型トランジスタは、ウェルと逆導電の不純物をチャネルドープすることにより形成されるデプレッション型トランジスタであって、かつ、MOS型トランジスタのチャネル領域が、多結晶シリコン層もしくはアモルファスシリコン層からなる第1のチャネル領域と、単結晶シリコン層からなる第2のチャネル領域と、が順次設けられた積層構造を有しており、更に、第1のチャネル領域が、チャネルドープされた領域とウェルとの境界に形成されるPN接合よりも表面側に位置している。

(もっと読む)

調光検知MOSFETトランジスタならびにその製造方法

【課題】光センサならびに調光装置の機能を達成し、スペースを減少させる部品構造を形成する。

【解決手段】調光検知MOSFETトランジスタであって、第一方向に沿って伸張するチャネル130により分離された2のソースおよびドレイン領域を有し、光の照射を受ける基板100と、第一方向と実質的に垂直な第二方向に沿って伸張するゲート導電性の梁(gate conductive beam)140であり、かかる梁は、少なくとも一の支持領域上で、その2つの端部のそれぞれにおいて固定され、チャネル領域130の上に位置し、当該ゲート梁は、ゲート電圧とバルク電圧間の差であって、当該梁を曲げてチャネルの表面に近づけさせるものにより制御されるその湾曲に基づいて、チャネル130に達する光にプログレッシブ変調を実行するよう、ほぼ不透明で柔軟であるゲート導電性の梁を備える。

(もっと読む)

電界効果半導体装置

【課題】HEMTの漏れ電流を低減すること及び集積度を高めることが困難であった。

【解決手段】HEMT又はこれに類似の電界効果半導体装置は、第1の半導体層(3)と、第1の半導体層(3)に2次元電子ガス層を生じさせるために第1の半導体層(3)の一部上に配置された第2の半導体層(4)と、第1の半導体層(3)の主面(14)上に配置された第3の半導体層(5)と、第3の半導体層(5)の上に配置され且つ第3の半導体層(5)よりも低い抵抗率を有している第4の半導体層(6)と、第2の半導体層(4)の上に配置された第1の主電極(7)と、第4の半導体層(6)の上に配置された第2の主電極(8)と、第3の半導体層(5)の側面を被覆している絶縁膜(9)と、絶縁膜(9)を介して第3の半導体層(5)に対向配置されたゲート電極(10)とを備えている。

(もっと読む)

半導体装置

【課題】上層配線と下層配線との間の絶縁耐圧を一定以上に維持しつつ、それ以外の部分の層間絶縁膜の膜厚を小さくすることができる、半導体装置を提供する。

【解決手段】半導体基板1上には、ソース配線10が形成されている。ソース配線10上には、第2層間絶縁膜12および第3層間絶縁膜14が積層されている。第3層間絶縁膜14上には、ドレイン配線15が形成されている。ドレイン配線15は、平面視でソース配線10と交差し、少なくともこの交差部分が第3層間絶縁膜14から浮いた状態で離間している。第3層間絶縁膜14とドレイン配線15との間には、隙間16が生じている。この隙間16には、低誘電率体17が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】FETチェックトランジスタを用いて電気的特性を測定される半導体装置を小型化する。

【解決手段】半導体装置100は、その製造過程において、ゲート用パッド部140g、ソース用パッド部140s、およびドレイン用パッド部140dを覆うパッシベーション膜115を形成する前に、ゲート用パッド部140g、ソース用パッド部140s、およびドレイン用パッド部140dを用いて電気的特性の測定がなされるように構成されたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】水素原子の拡散による特性変動が少ない半導体装置を提供することを課題とする。

【解決手段】半導体基板上に、ゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板及び前記ゲート電極上に第一のシリコン窒化膜を形成する工程と、前記ゲート電極をマスクとして前記第一のシリコン窒化膜を介して不純物注入することにより前記半導体基板の表面層に拡散領域を形成する工程と、前記第一のシリコン窒化膜上に第二のシリコン窒化膜を形成する工程とを含み、前記第一のシリコン窒化膜が、前記第二のシリコン窒化膜より水素含有量が小さいことを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置

【課題】本発明は、高耐圧の特性を有し、且つ製造プロセスを簡略化できるSOI基板の半導体層をフィン状に加工したトランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、埋め込み酸化膜1上に、半導体層2とゲート電極5と、ソース領域8及びドレイン領域7と、ボディ領域9とを備えている。埋め込み酸化膜1は、基板上に設けられ、半導体層2は、埋め込み酸化膜1上にフィン状に形成されている。ゲート電極5は、半導体層2の一方の側面上にゲート絶縁膜を介して形成されている。ソース領域8及びドレイン領域7は、ゲート電極5を挟むように半導体層2内に形成され、ボディ電位を取るボディ領域9は、ゲート電極5が形成された半導体層2の側面の反対側の側面に設けられている。

(もっと読む)

201 - 220 / 403

[ Back to top ]