Fターム[5F140BJ05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 最下層材料 (3,069) | 金属 (2,883)

Fターム[5F140BJ05]の下位に属するFターム

合金 (116)

高融点金属 (492)

金属シリサイド (1,738)

金属化合物(窒化物、酸化物) (134)

Fターム[5F140BJ05]に分類される特許

141 - 160 / 403

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

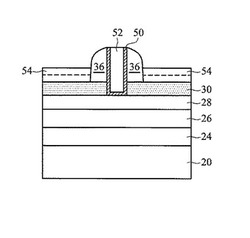

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

半導体装置及びその製造方法

【課題】 低いオン抵抗を維持しつつ、従来構成よりも更に耐圧低下を抑制したLDMOSトランジスタ及びその製造方法を提供する。

【解決手段】 P型基板1上に形成された、N型ウェル2と、ウェル2内に形成されたP型ボディ領域6と、ウェル2内においてボディ領域6よりも深い位置に形成されたP型の埋め込み拡散領域4と、ボディ領域6内に形成されたN型のソース領域9と、ウェル2内において、素子分離領域を介してボディ領域6と離間して形成したN型のドリフト領域7と、ドリフト領域7内に形成されたN型のドレイン領域10と、少なくとも前記ボディ領域9の一部上方、及びボディ領域9とドレイン領域10に挟まれた位置におけるウェル領域2の上方にわたってゲート絶縁膜を介して形成されたゲート電極7と、有し、ドリフト領域7並びにドレイン領域10が、ボディ領域6を取り囲むようにリング状に形成されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】量産性に優れた実用的なプロセスを用いて、炭化珪素基板と二酸化珪素膜との間の界面準位を大幅に低減することができ、デバイスとしての信頼性と電気特性が優れた炭化珪素半導体装置を提供する。

【解決手段】二酸化珪素膜51の形成後、CVD法により、二酸化珪素膜51上に酸窒化珪素膜61を形成する。その後、酸窒化珪素膜61が堆積された炭化珪素基体10を窒化処理反応炉に導入し、窒素酸化物ガス雰囲気中で窒化処理を行う。

(もっと読む)

電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

半導体装置

【課題】トランジスタ本来の特性を出すことが可能な配線パターンの第1配線層を有する半導体装置を提供する。

【解決手段】半導体基板10の表面に延在し、所定間隔を有して交互に配置されたソース領域20及びドレイン領域30と、該ソース領域20又は該ドレイン領域30とコンタクトホール60、60aを介して接続されたフィンガー状の配線75、75a、75bを複数含む第1配線層70、70aと、該第1配線層70、70aとスルーホール80、80aを介して接続された第2配線層90とを有する半導体装置であって、前記第1配線層70、70aは、前記スルーホール80、80aが形成されないスルーホール非形成領域74、74a、74bの配線幅が、前記スルーホール80、80aが形成されるスルーホール形成領域73、73a、73bの配線幅よりも広い前記フィンガー状の配線75、75a、75bを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子サイズの拡大を伴うことなくゲート−ドレイン間(又はゲートソース間)耐圧を確保できる半導体装置とその製造方法を提供する。

【解決手段】基板表面のドレイン側又はソース側の少なくとも一方にLOCOS膜を形成する工程と、基板表面に、LOCOS膜に接続されたゲート酸化膜を形成する工程と、ゲート酸化膜とLOCOS膜を覆う導電膜の形成工程と、導電膜の端部がLOCOS膜の上に位置するように導電膜をエッチングするゲート電極の形成工程と、ゲート電極の端部とエッチング端面が揃うようにLOCOS膜とゲート酸化膜をエッチングして、基板表面のLOCOS膜を除去した部分に凹部を形成する工程と、ゲート電極の側壁を覆い、その底面が凹部の底面と接するようにサイドウォールスペーサを形成する工程と、基板表面のゲート電極とサイドウォールスペーサを挟む位置に不純物を添加して、ドレイン及びソース領域の形成工程と、を含む。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのリーク電流を防止できる電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタによれば、WN/Alドレイン電極109がドレイン電極109の下のn+型領域(拡散領域)112を介してGaNチャネル層104にショットキー接合されている。これにより、従来の熱処理によりドレイン電極にオーミックコンタクトを形成する場合と異なり、ドレイン電極109下へメタルが侵入することを回避できる。よって、このメタル侵入が発生するために生じるリーク電流を低減することが可能であり、電界効果型トランジスタにおける破壊電圧を向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSトランジスタのドリフト領域面におけるキャリア蓄積層が制御されるように構成された半導体装置及びその製造方法を提供すること。

【解決手段】p型基板1と、p型基板1上に形成されたn型ウェル6と、n型ウェル6に形成されたpボディ領域18と、pボディ領域18に形成されたp+型ソース領域27及びn+型ソース領域25と、n型ウェル6に形成されたn+型ドレイン領域26と、pボディ領域18とn型ウェル6との上部に形成されたゲート電極である導電性ポリシリコン層15とを備えている。ゲート電極15の直下には、厚みの異なる反転層制御用ゲート酸化膜(第1ゲート酸化膜)14と蓄積層制御用ゲート酸化膜12とを有し、膜厚が厚い蓄積層制御用ゲート酸化膜12の下面は、n型ウェル6上に、反転層制御用ゲート酸化膜14と同一面に形成されている。

(もっと読む)

絶縁ゲート型電界効果トランジスタ回路

【課題】温度変化による動作特性の低下を抑制する電界効果トランジスタ回路を提案する。

【解決手段】本発明の例に係る絶縁ゲート型電界効果トランジスタ回路は、拡散層をそれぞれ備える第1のソース/ドレイン4S,4Dと、チャネル領域上に設けられる第1のゲート絶縁膜2と、前記第1のゲート絶縁膜2上に設けられる第1のゲート電極3とを有する第1の電界効果トランジスタTrと、半導体基板1とショットキー接合を形成する金属層をそれぞれ備える第2のソース/ドレイン14S,14Dと、チャネル領域上に設けられる第2のゲート絶縁膜12と、第2のゲート絶縁膜12上に設けられる第2のゲート電極13と、を具備し、第1のドレイン4Dと第2のドレイン14Dとが並列に接続される。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

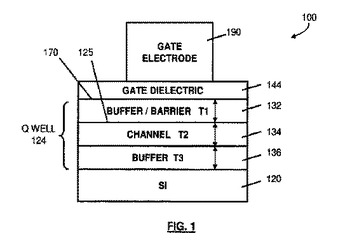

電界効果トランジスタの量子井戸に設けられる変調ドーピングハロー、それを用いて製造された装置、および、その利用方法

【解決手段】 量子井戸(QW)層を半導体デバイス内に設ける。QW層について、QW層の下方に設けられる障壁構造にベリリウムドーピングハロー層が設けられる。当該半導体デバイスでは、QW層の下方および上方にそれぞれ、InGaAsの下部障壁層および上部障壁層が設けられている。当該半導体デバイスではさらに、ゲートリセスにおいて、InPスペーサ第1層上にHigh−kゲート誘電体層が設けられる。QW層を形成するプロセスでは、オフカット半導体基板を利用する。

(もっと読む)

静電気放電保護装置及び方法

【課題】静電気放電保護装置及び方法を提供する。

【解決手段】本発明の実施例は、静電気放電(ESD)保護装置、及び、ESD保護装置を形成する方法に関する。一実施例は、ESD保護装置で、基板に配置されたpウェルと、基板に配置されたnウェルと、基板中のpウェルとnウェルの間に配置された高電圧nウェル(HVNW)と、pウェルに配置されたソースn+領域と、nウェルに配置された複数のドレインn+領域と、からなる。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ(MOSFET)100は、基板101上に、p−GaNからなるチャネル層104、電子供給層106、電子供給層よりもバンドギャップエネルギーが小さい表面層107を順次積層し、電子供給層および表面層の一部をチャネル層に到る深さまで除去してリセス部108を形成したものである。表面層上には、リセス部を挟んでソース電極109およびドレイン電極110が形成され、表面層上およびチャネル層表面を含むリセス部内表面上にゲート絶縁膜111が形成され、さらにリセス部においてゲート絶縁膜上にはゲート電極112が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の侵食を抑制し、FETの故障や不良の発生を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層15を形成する工程と、GaN系半導体層15上に酸化アルミニウムからなるゲート絶縁膜18を450℃以下の成膜温度で形成する工程と、ゲート絶縁膜18の上面に保護膜19を形成する工程、ゲート絶縁膜18を熱処理する工程、及びゲート絶縁膜18をプラズマ処理する工程のいずれか一つと、前記いずれか一つの工程の後に、ゲート絶縁膜18を形成する工程の後のアルカリ溶液を用いた処理を実行する工程と、前記ゲート絶縁膜18上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の同一サイズの半導体装置と比較してゲート耐圧を向上させるとともに、素子分離層をバーズビークを含まない構造とすることにより素子分割領域の面積を縮小し、素子の微細化を図ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板表面に素子形成領域から素子分割領域に亘って延在するLOCOS膜を形成する。素子形成領域内の半導体基板上にLOCOS膜に接続されたゲート酸化膜を形成する。LOCOS膜およびゲート酸化膜を覆うように導電膜を形成する。導電膜を部分的にエッチングしてゲート酸化膜およびLOCOS膜の一部を覆うゲート電極を形成する。導電膜のエッチングによって露出したLOCOS膜を部分的にエッチングしてLOCOS膜を素子分離層とゲート酸化膜の端部を構成する高膜厚部とに分割する。LOCOS膜のエッチングによって露出した半導体基板の表面にイオン注入を行ってゲート電極を挟む位置にドレイン領域およびソース領域を形成する。

(もっと読む)

半導体装置の製造方法

【課題】Siおよびこれと同族元素であるGe,Cなどの組合せを用いて、低消費電力で高速なMOSFETを有する半導体装置の製造方法を提供する。

【解決手段】Si層1と、その上に形成されたMOSFETのゲート電極16と、Si層1に形成されたソース領域14及びドレイン領域15と、それらの間の領域に形成されるチャネル領域とを有する半導体装置の製造方法において、ソース領域14またはドレイン領域15が形成される領域のSi層1を選択的にエッチングし、形成された溝内にSiGeを選択成長させる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

141 - 160 / 403

[ Back to top ]