Fターム[5F140BJ05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 最下層材料 (3,069) | 金属 (2,883)

Fターム[5F140BJ05]の下位に属するFターム

合金 (116)

高融点金属 (492)

金属シリサイド (1,738)

金属化合物(窒化物、酸化物) (134)

Fターム[5F140BJ05]に分類される特許

161 - 180 / 403

電界効果トランジスタの不動態化のための方法

【課題】少なくとも1つのソース電極と、ドレイン電極と、ゲート電極とを有する電界効果トランジスタの不動態化において、従来技術の問題点を解決する。

【解決手段】少なくとも1つの化学的感受性の電極を有する半導体構成素子の不動態化のために、少なくとも、該化学的感受性の電極を、ガラス層もしくはガラスセラミック層の施与によって覆い隠す。

(もっと読む)

リサーフ構造を用いた電界効果トランジスタ

【課題】炭化珪素基板上に、高耐圧で低抵抗なMOS電界効果トランジスタを形成する。

【解決手段】第1の導電型を持つ炭化珪素半導体の活性層(1)と、該活性層の表面部分に形成された第2の導電型のソース領域(4)と、該ソース領域から間隔をおくように形成された第2の導電型のドリフト領域(2)と、該ドリフト領域の表面部分に形成された第1の導電型の電界緩和領域(6)と、第2の導電型のドレイン領域(3)と、ソース領域とドリフト領域とで挟まれた領域の上に形成されたゲート絶縁膜(11)及びゲート電極(12)と、を具備する。電界緩和領域(6)は、互いの投影方向においてゲート電極(12)と重なる部分を持ち、ドリフト領域上のゲート電極(12)の端点の位置(II)から電界緩和領域のドレイン側の端点(IV)までの長さは、電界緩和領域の該端点(IV)からドレイン領域の端点(I)までの長さよりも短い。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】 従来の構造よりさらに安定した電気的特性を実現しうる横型MOSトランジスタを提供する。

【解決手段】 P型の半導体基板10内において方向d1に延伸するP型のボディ領域15、ボディ領域15と離間して形成されたN型のドレイン領域11、ボディ領域15内に形成された高濃度P型のボディコンタクト領域21及びN型のソース領域16、ドレイン領域11内に形成された高濃度N型のドレインコンタクト領域12、並びにソース領域16とドレインコンタクト領域12の間に形成されたP型の拡散領域13を備え、拡散領域13は、ドレイン領域11内においてボディ領域15と離間した状態で方向d1に延伸して形成される主領域13aと、主領域13a内のボディ領域15と対向する外周端の一または離散した複数の一部領域からボディ領域15に向かう方向にボディ領域15または半導体基板10と連絡する位置まで突出する突出領域13bとを有する。

(もっと読む)

窒化ガリウム系化合物半導体層の形成方法、移設方法、及び窒化ガリウム系化合物半導体層が接合されたシリコン基板

【課題】比較的結晶欠陥の少ない窒化ガリウム系化合物半導体層を比較的低コストで得ることができる技術を提供する。

【解決手段】サファイア基板10上に、SiO2層13を形成し、層13を部分的に除去してサファイア基板の露出部を形成し、露出部を持つサファイア基板上に、非晶質窒化ガリウム系化合物半導体を堆積し、層13上の非晶質窒化ガリウム系化合物半導体を蒸発させ、サファイア基板の露出部上に非晶質窒化ガリウム系化合物半導体の核を形成し、核のサイズ増大、合体、結晶成長、層13上への横方向結晶成長、平坦表面形成などを経て、サファイア基板上に窒化ガリウム系化合物半導体層20を形成し、サファイア基板10の露出部上の窒化ガリウム系化合物半導体層を除去して分離溝25を形成する。サファイア基板上の窒化ガリウム系化合物半導体層20は他の基板に移設される。

(もっと読む)

グラファイト薄膜の切断方法、グラファイト薄膜を備える積層基板、およびこれを用いる電界効果トランジスタ

【課題】複雑な加工技術を用いることなく、グラファイト薄膜をナノスケール幅に切断することができるグラファイト薄膜の切断方法を提供すること。

【解決手段】複数の段差部1aを有する基板1の表面に、グラファイト薄膜2を設ける工程と、グラファイト薄膜2が設けられた基板1を、酸素含有雰囲気下で加熱して、グラファイト薄膜2を段差部1aの位置で切断する工程とを含む、グラファイト薄膜の切断方法。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置

【課題】チップの占有面積を有効に活用する。

【解決手段】P型半導体基板11上にN型エピタキシャル層12が形成され、LDMOSとJFETに共通なドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成され、ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ボディ領域15とP型素子分離領域13との間にJFETのソースとなるN型領域が形成される。ドレインに正のドレイン電圧が印加されると、PN接合が逆バイアスされ、ボディ領域15と分離領域13と半導体基板11とから空乏層が延び、JFETのチャネルを制御する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 フィールド酸化膜の厚さによらず、第1不純物領域−第2不純物領域間(たとえば、ソース−ドレイン間)における電位分布の偏りを抑制することのできる半導体装置およびその製造方法を提供すること。

【解決手段】 半導体装置1におけるLDMOSFET6において、エピタキシャル層3の表面におけるドレイン領域11とボディ領域7との間の部分に、ボディ領域7と間隔を空けてフィールド酸化膜12を形成する。そして、フィールド酸化膜12に、ドレイン領域11およびゲート電極14と間隔を空けて形成されたフローティングプレート17を埋設する。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース−ドレイン方向に垂直な方向における耐圧低下を防止し、過電圧、過電流に対する耐性も増大させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】P型半導体基板201と、N型拡散領域202と、N型拡散領域202内に形成されたP型ボディー領域206と、N型拡散領域202内に形成されたP型埋込み拡散領域204と、P型ボディー領域206内に形成されたN型ソース領域208及びP型ボディーコンタクト領域209と、N型拡散領域202内に形成されたN型ドリフト領域207と、N型ドリフト領域207内に形成されたN型ドレイン領域210と、P型ボディー領域206上に形成されたゲート絶縁膜とその上に形成されたゲート電極211と、を備え、ソース−ドレイン方向に垂直な断面において、P型埋込み拡散領域204が、ゲート電極211よりもP型ボディー領域206から離れた位置にまで延在される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、p型不純物を、異なる注入エネルギーでn型半導体層内部と表面に多段注入し、熱処理により同時に拡散してp型ウェル領域とする。これにより、表面からある程度の深さ(5μm程度)までの不純物プロファイルが略平坦なp型ウェル領域を得ることができ、その表面に形成されるチャネル層の特性変動も抑制できる。

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

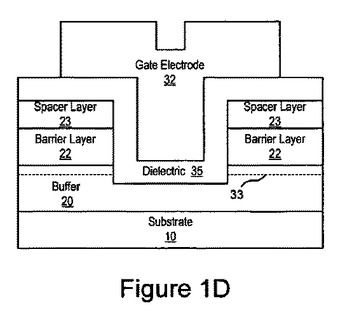

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】横型二重拡散MOSトランジスタのオン抵抗を上昇させることなく、オン状態でのソース-ドレイン領域間の耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】p型半導体基板上7に形成された横型二重拡散MOSトランジスタを構成において、ソース領域となる高濃度n型拡散層9に接するように、低濃度p型ウエル層11の電極となる高濃度p型拡散層10を形成する。上記高濃度p型拡散層10は、ソースコンタクト部4sの内側に位置する基部10a(十字形の交差部分)と、上記基部10aからソースコンタクト部4sの外側に延びた複数の延伸部10bとを有する。

(もっと読む)

MOSトランジスタ、CMOS及びこれを用いたモータ駆動用半導体集積回路装置

【課題】本発明は、製造工程の大きな変更もなく、1枚のマスクの変更のみで駆動時の出力波形の立ち上がりの時間的変化率を緩やかにできるMOSトランジスタを提供することを目的とする。

【解決手段】半導体基板上80に所定のゲート幅Wを有して延在する複数のゲート10が略平行に配置され、該ゲートの両側にソース20とドレイン30が交互に配置された複数のトランジスタセルを含むMOSトランジスタ100、100aであって、

前記ゲート10の両端部11、12と平面視的に重なり、前記ゲート10の両端部11、12から同電位の供給が可能に配置されたゲート配線層70を有し、

該ゲート配線層70と前記ゲート10の端部とを電気的に接続するゲートコンタクト40が、前記ゲート10の端部11、12の片側のみに設けられたトランジスタセルを含むことを特徴とする。

(もっと読む)

高電子移動度トランジスタの製造方法

【課題】トラッピングを少なくするためにAlGaN層を薄くし、またゲート漏洩を減少させるために層を追加して最大駆動電流を増加させるようにする。

【解決手段】基板88を金属有機化学気相成長反応器80中に置く工程と、基板88上に高比抵抗のGaN層20を形成するために、原料ガスを金属有機化学気相成長反応器80の反応チャンバー82中に流す工程と、GaN層20上に、GaN層20よりも広いバンドギャップを有するAlGaNバリア半導体層18を形成するために、原料ガスを反応器チャンバー82中に流す工程と、AlGaNバリア半導体層18上に絶縁層24を形成するために原料ガスを反応器チャンバー82中に流す工程と、反応チャンバー82を冷却する工程と、堆積された層を備える基板88を前記反応チャンバー82から取り出す工程とを有する。

(もっと読む)

トランジスタ

【課題】トラッピングを少なくするためにAlGaN層を薄くし、またゲート漏洩を減少させるために層を追加して最大駆動電流を増加させるようにする。

【解決手段】高比抵抗半導体層20と、この高比抵抗半導体層20上に設けられたバリア半導体層18と、このバリア半導体層18に接触するするとともに、バリア半導体層18の表面部を被覆していないソースおよびドレインコンタクト13,14と、バリア半導体層18の被覆されていない表面上に設けられた絶縁層24と、この絶縁層24上に設けられ、ゲート漏洩のバリアを形成するゲートコンタクト16とを備えている。

(もっと読む)

小型化可能な量子井戸デバイスおよびその製造方法

【課題】小型化可能な、量子井戸デバイスおよびその製造方法を提供する。

【解決手段】量子井戸QWデバイスは、基板1を覆う量子井戸領域QW、量子井戸領域の一部を覆うゲート領域G、ゲート領域に隣接するソース領域Sおよびドレイン領域Dを含む。量子井戸領域は、第1バンドギャップを有する半導体材料を含むバッファ構造2と、バッファ構造2を覆い、第2バンドギャップを有する半導体材料を含むチャネル構造3と、チャネル構造3と接する第3バンドギャップを有するアンドープの半導体材料を含むバリア構造4とを含み、第1バンドギャップと第3バンドギャップは、第2バンドギャップより広い。ソース領域Sとドレイン領域Dは、それぞれゲート領域Gに対してセルフアラインであり、第4バンドギャップを有する半導体材料を含み、第4バンドギャップは第2バンドギャップより広い。

(もっと読む)

バルク基板上に形成されたダブルゲート及びトライゲートトランジスタ及びそのトランジスタを形成するための方法

【解決手段】

FinFETS及びトライゲートトランジスタのような三次元トランジスタ構造が、強化されたマスキング形態によって形成することができ、それによりバルク半導体材質内での自己整合手法によるドレイン及びソース区域(211D,211S)、フィン(210)並びに分離構造(208A)の形成が可能になる。基本フィン構造(210)を画定した後、プレーナトランジスタ構造の高度に効率的な製造技術を用いることができ、それにより三次元トランジスタ構造の総合的な性能を更に高めることができる。

(もっと読む)

161 - 180 / 403

[ Back to top ]