Fターム[5F140BJ05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 最下層材料 (3,069) | 金属 (2,883)

Fターム[5F140BJ05]の下位に属するFターム

合金 (116)

高融点金属 (492)

金属シリサイド (1,738)

金属化合物(窒化物、酸化物) (134)

Fターム[5F140BJ05]に分類される特許

81 - 100 / 403

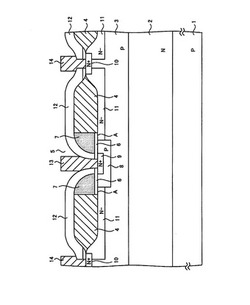

半導体装置及びその製造方法

【課題】LDMOSトランジスタに係る半導体装置の高速動作を可能とする。

【解決手段】P型ウエル層3の表面に形成された複数の素子分離膜4の中央部に開口溝5を形成する。開口溝5の側壁から開口溝5の内側に向かってゲート絶縁膜6を介して延在するゲート電極7を形成する。ゲート電極7をマスクにしてセルフアラインでボロンの斜めイオン注入により開口溝5内のP型ウエル層3にP型ボディ層8を形成する。

ゲート電極7をマスクに砒素のイオン注入によりP型ボディ層8にN+型ソース層9を、同時に2つの素子分離膜4間のP型ウエル層3にN+型ドレイン層10を形成する。素子分離膜4の下方のP型ウエル層3にP型ボディ層8の端部からN+型ドレイン層10に延在するN−型ドリフト層を形成する。この際、P型ボディ層8の端部から開口溝5の側壁下部までの領域AのN−型ドレイン層11の幅をできるだけ小さくなるよう制御する。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Ga2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

電界効果半導体装置の製造方法

【課題】半導体装置を構成する半導体層の表面上にAlOx層を安価に形成でき、且つAlOx層を厚膜化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体層2、3、4と、前記窒化物系化合物半導体層2、3、4上に隣接して形成された酸化アルミニウム層7と、を備える半導体装置の製造方法であって、

前記窒化物系化合物半導体層2、3、4上に多結晶又は非晶質の窒化アルミニウム層6を形成する第1の工程と、前記多結晶又は非晶質の窒化アルミニウム層6を熱酸化して前記酸化アルミニウム層7を得る第2の工程と、を備えることを特徴とする半導体装置の製造方法。

(もっと読む)

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

半導体装置

【課題】シリコン基板裏面をソース電極として使用するLDMOSFETにおいて、出力効率向上のため、基板抵抗を下げようとして高濃度ボロンドープ基板を用いると、ソースドレイン間のリーク不良が、多発することが、本願発明者等によって明らかにされた。更に、この不良解析の結果、ソース不純物ドープ領域からP型エピタキシ層を貫通してP型基板に至るP型ポリシリコンプラグに起因する不所望な応力が、このリーク不良の原因であることが明らかにされた。

【解決手段】本願発明は、LDMOSFETを含む半導体装置であって、LDMOSFETのソース不純物ドープ領域の近傍の上面から下方に向けてエピタキシ層内をシリコン基板の近傍まで延び、前記エピタキシ層内にその下端があるシリコンを主要な成分とする導電プラグを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主表面2Aを有し、炭化珪素からなる基板2と、基板2の主表面2A上にエピタキシャル成長により形成され、炭化珪素からなるp型層4と、p型層4の表面に接触するように形成された酸化膜8とを備えている。そして、p型層4と酸化膜8との界面から10nm以内の領域における窒素原子濃度の最大値は1×1021cm−3以上となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】界面準位を低減しつつ、電荷トラップに起因するヒステリシスを抑制できる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置200は、GaNを含む半導体層101を表面の少なくとも一部に有する基板(半導体基板100)と、半導体層101と接するように半導体基板100上に設けられており、窒素を含まず、Alを含む酸化金属層からなる第1のゲート絶縁層(Al2O3膜114)と、Al2O3膜114上に設けられており、SiおよびOを含む第2のゲート絶縁層(SiO2膜116)と、SiO2膜116上に設けられたゲート電極118と、を備え、ゲート電極118の下面は、SiO2膜116に接しており、Al2O3膜114の膜厚は、SiO2膜116の膜厚より薄い。

(もっと読む)

可動ゲート型電界効果トランジスタ

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

半導体集積装置の製造方法及び半導体集積装置

【目的】製造工程数を増加させることなく、高い耐圧の半導体集積装置を製造することが可能な半導体集積装置の製造方法、及び半導体集積装置を提供することを目的とする。

【構成】半導体基板の表面に形成されている拡散領域に接するボディ領域と、埋込拡散層との間に、半導体基板よりも電気抵抗が低いシンカー層を設ける。又、かかるシンカー層を形成すべく半導体基板表面に設けるレジスト膜に対して、その側面と半導体基板の底面との交叉角が90度未満となるテーパー加工処理を施す。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

高導電性のソース/ドレイン接点を有するIII族窒化物トランジスタ及びその製造方法

【課題】III族窒化物トランジスタのドレイン及びソース接点と、下位のドレイン及びソース領域の各々との間の抵抗を低減させる。

【解決手段】ゲート、ソース、及びドレイン領域上に延在するフィールド誘電体240にトレンチをエッチングする工程と、ゲート、ソース、及びドレイン領域上にゲート誘電体270を形成する工程と、ゲート誘電体上270にブランケット拡散バリア272を形成する工程と、ソース及びドレイン領域からブランケット拡散バリア272を除去する工程と、ゲート誘電体270をソース及びドレイン領域から除去し、ソース及びドレイン領域をほぼ露出させる工程とを含む。次いで、ソース及びドレイン領域に接点金属290を堆積することにより、オーミック接点を形成する。

(もっと読む)

81 - 100 / 403

[ Back to top ]