Fターム[5F140BJ11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層以上 (955)

Fターム[5F140BJ11]に分類される特許

121 - 140 / 955

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】チャネル領域の低抵抗化を図りながら、ノーマリオフを実現する。

【解決手段】半導体装置を、キャリア走行層3及びキャリア供給層5を含む窒化物半導体積層構造と、窒化物半導体積層構造の上方に設けられ、活性化領域10と不活性領域10Aとを有するp型窒化物半導体層6と、p型窒化物半導体層の不活性領域上に設けられたn型窒化物半導体層7と、p型窒化物半導体層の活性化領域の上方に設けられたゲート電極13とを備えるものとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

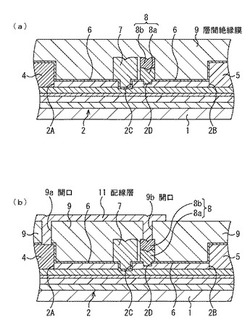

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

半導体デバイスおよび半導体デバイス製造方法

【課題】III族窒化物半導体では、p型不純物を高濃度にイオン注入すると、結晶品質が低下してしまう。結晶品質が低下するとオフ電流が増加して、電子デバイス特性が低下する可能性がある。このため、III族窒化物半導体では、p+層を形成することが困難であった。

【解決手段】III族窒化物半導体にドープされるとp型半導体になるp型不純物、および金属を有する合金からなる合金層と、合金層の下に接して形成され、III族窒化物半導体からなり、p型不純物が一部に拡散している半導体層と、合金層上に形成され、p型不純物の拡散係数が、半導体層より小さい拡散防止層と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】DMOSトランジスタのセルピッチを短縮しながらもオン抵抗値を高めることがない、半導体装置、半導体装置の製造方法を提供することを目的とする。

【解決手段】第1の極性を有するN型ウェル202上に形成されたゲート101、ゲート101の間に形成されたソース102、N型ウェル202においてソース領域を含む領域に形成されたP+型ボディ不純物領域105、ゲート101のそれぞれの外側に設けられたドレイン104を含む半導体装置において、ソース102は、一方向に沿って交互に配置されるN+型ソース102b及びP+型不純物領域102aを含み、P型ボディ不純物領域105内であって、かつ、ゲート101によってチャネルが形成される領域とP+型不純物領域102aとの間にN+型ソース低抵抗領域110を設ける。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

121 - 140 / 955

[ Back to top ]