Fターム[5F140BJ11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層以上 (955)

Fターム[5F140BJ11]に分類される特許

941 - 955 / 955

半導体装置及び半導体装置の製造方法

【課題】 第1層配線と、拡散層あるいはゲート電極との層間容量を抑えつつ、拡散層あるいはゲート電極に確実に接続するコンタクトプラグを形成する。

【解決手段】 基板上方に形成されたゲート電極と、ゲート電極の両側に形成された拡散層とを有する半導体装置において、一端において、ゲート電極の上面に接し、かつ、他端が、ゲート電極上面よりも、基板に近い位置に伸びる導電体膜を形成する。そして、基板上に、ゲート電極と、導電体膜とを埋め込む層間絶縁膜を形成し、この層間絶縁膜を貫通し、導電体膜の、ゲート電極上面よりも基板に近い位置において、導電体膜に接続する第プラグを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】静電破壊耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極とドレイン領域とソース領域とを有する半導体装置であって、ドレイン領域は、ゲート電極の第1の側に形成された第1導電型の第1の不純物拡散領域18aと;第1の不純物拡散領域より深く形成された第1導電型の第2の不純物拡散領域20aと;第1の不純物拡散領域より浅く形成され、不純物拡散層より不純物濃度が高い第1導電型の第3の不純物拡散領域28a、28bと;第3の不純物拡散領域上に形成され、ドレインコンタクト部22Dに接続されるシリサイド膜32a、32bとを有し、ドレインコンタクト部とサイドウォール絶縁膜との間にシリサイド膜が形成されていない領域が存在しており、ドレインコンタクト部の下方の半導体基板内に第2の不純物拡散領域が形成されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

半導体装置の製造方法

【課題】更なる微細化を促進できる半導体装置の製造方法を提供すること。

【解決手段】 第1の半導体層1上に、第1半導体層1よりも絶縁化し難い第2半導体層3を形成する工程と、第2半導体層3の上面から第1半導体層1にかけて、第2半導体層3、及び第1半導体層1を露出させる溝7を形成する工程と、溝7から露出する第1半導体層1、及び第2半導体層3を絶縁化し、溝を、絶縁化した第1半導体層9で閉じる工程とを具備する。

(もっと読む)

低ソース・ドレイン容量用高周波トランジスタ・レイアウト

ゲート電極と櫛形ドレイン及びソース電極を有し、櫛形ドレイン電極の複数の指が櫛形ソース電極の複数の指と互い違いに配置されており、ソース及びドレイン電極が多層(110,120,130,149)を有するRF電界効果型トランジスタ。互い違いの量が各層で異なることにより、多層によりもたらされる低電流密度の効果のすべては失うことなく、最適化、特に、低寄生容量が可能となる。指を短くすることにより、ゲート電極から離間した層において互い違いが低減される。互い違いの低減は、最小容量のために急激な互い違いの低減、最小横方向電流密度のためにより緩やかな互い違いの低減により、最適化される。これが、より高温度又はより高入力バイアス電流においても動作を可能にし、一方、依然として、エレクトロマイグレーションの条件を満たす。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

歪み半導体層の製造方法、半導体装置の製造方法、およびそのような方法で使用するのに適した半導体基板

本発明は、半導体歪み層の製造方法と、シリコンの半導体本体(11)に、その表面において、シリコンおよびゲルマニウムの混晶の格子と、格子が実質的に緩和されるような厚さとを有する第1の半導体層(1)が設けられ、かつ第1の半導体層(1)の上に、歪みシリコンを含む第2の半導体層(2)が設けられ、その層(2)内に半導体装置(10)の一部が形成され、半導体装置(10)を形成するのに必要な後続の処理中に、歪みシリコン層(2)の有効厚さの低減を回避するための手段が取られ、前記手段が、シリコンおよびゲルマニウムの混晶の格子を有する第3の層(3)を使用することを含む、半導体装置(10)の製造方法とに関する。本発明によれば、第3の層(3)は、薄く、かつ第1の半導体層(1)および第2の半導体層(2)の境界面に近接して第2の層(2)内に位置付けられる。このようにして、歪みシリコン層(2)の結果として得られる厚さは、後続のMOSFETの形成の後に増加されることができ、その結果、より良好な高周波特性を備えたMOSFETが得られる。本発明は、また、本発明による方法で得られる装置、およびそのような方法で使用するのに適した半導体基板構造を含む。  (もっと読む)

(もっと読む)

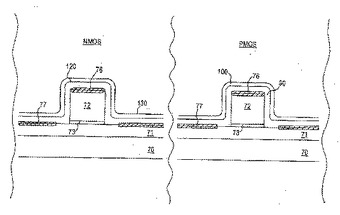

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

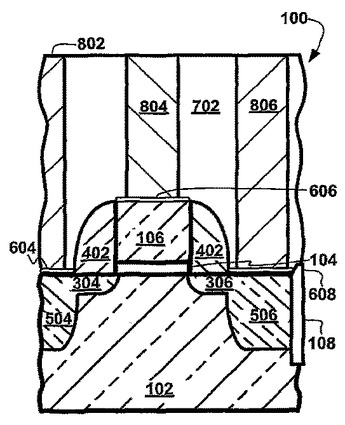

集積回路技術における低応力の側壁スペーサ

半導体基板(102)に集積回路の形成方法(900)を提供する。半導体基板(102)上にゲート絶縁膜(104)が形成され、このゲート絶縁膜(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(304)(306)が形成される。低出力プラズマ化学気相成長法プロセスを使用して、ゲート(106)の周りに側壁スペーサ(402)を形成する。ソース/ドレイン接合部(304)(306)およびゲート(106)に、シリサイド(604)(606)(608)を形成し、半導体基板(102)上に層間絶縁層(702)をたい積する。その後、層間絶縁層(702)中にシリサイド(604)(606)(608)へのコンタクト(802)(804)(806)が形成される。  (もっと読む)

(もっと読む)

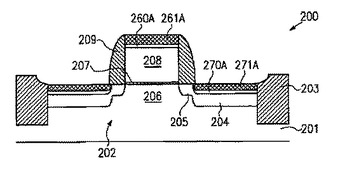

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

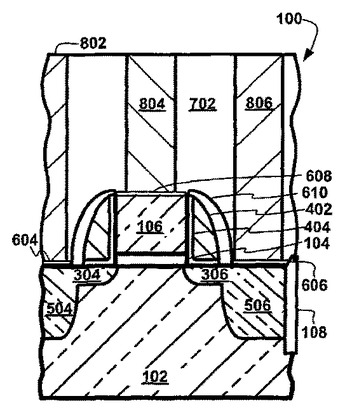

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

941 - 955 / 955

[ Back to top ]