Fターム[5F140BJ11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層以上 (955)

Fターム[5F140BJ11]に分類される特許

141 - 160 / 955

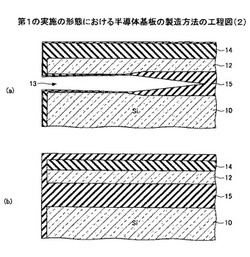

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

電界効果型トランジスター

【課題】ダイヤモンドFETにおいて、ドレイン電流特性を改善すること。

【解決手段】ダイヤモンド結晶層1の上に、高濃度ホウ素ドープダイヤモンド薄膜層102を成長する(図1(a))。次に、ソース電極およびドレイン電極として、Ti層131A、131B、Au層132A、132Bを順に蒸着する(図1(b))。次に、400℃でアニールを行いTiをダイヤモンドと反応させて、TiC層133A、133Bを形成する(図1(c))。最後に、ゲート部にAl2O3膜141を形成し、その上にAlゲート電極42を蒸着する(図1(d))。作製したダイヤモンドFETのドレイン電流特性は、ゲート電圧−3Vにおける最大ドレイン電流密度が600mA/mmとなり、従来技術による場合の約6倍に増加した。温度依存性に関しては、従来技術では室温から150℃付近でドレイン電流密度は急激に減少したが、本発明では900℃まで安定して動作した。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタにおいて、ホットエレクトロンのゲート絶縁膜へのトラップによるトランジスタ特性の経時劣化を減少させる。

【解決手段】N−−型の半導体層12の表面にボディ層19が配置されている。ボディ層19の表面にはN−型層23を含むソース層が配置されている。N−−型の半導体層12の表面には、N−型のドリフト層21が形成されている。このドリフト層21は、N型不純物濃度のピーク領域P1を有した第1の領域21Aと、この第1の領域21Aに隣接し、N型不純物濃度のピーク領域P1よりも深い位置にN型不純物濃度のピーク領域P2を有した第2の領域21Bとにより構成されている。第2の領域21Bの表面にはN+型のドレイン層25が形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置において、高温且つ高電圧下のスイッチング時においても電流コラプスによるオン抵抗の増大が生じないようにする。

【解決手段】基板1上には、バッファ層2、GaNからなるチャネル層3及びアンドープAlGaNからなるバリア層4が順次形成されている。チャネル層3は、該チャネル層3の下部にp型不純物層3aを有し、その上にアンドープ層3bを有している。バリア層4及びチャネル層3の端部が除去されており、露出したバリア層4及びチャネル層3の側面と接するように、それぞれソース電極5及びドレイン電極6が設けられている。バリア層4上におけるソース電極5とドレイン電極6との間の領域にはゲート電極7が設けられている。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

141 - 160 / 955

[ Back to top ]