Fターム[5F140BJ20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層目より上層の材料 (1,508) | 金属 (1,434) | 金属化合物(窒化物、酸化物) (313)

Fターム[5F140BJ20]に分類される特許

201 - 220 / 313

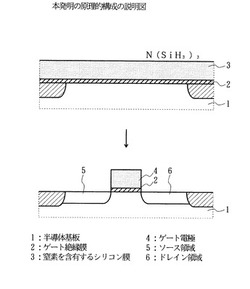

電界効果型半導体装置及びその製造方法

【課題】 電界効果型半導体装置及びその製造方法に関し、ゲート絶縁膜にダメージを与えることなく、少なくとも窒素を含有するとともにシリコンを主成分とする膜を組成制御性良く構成する。

【解決手段】 シリコンと、シリコンに対して5〜30原子数%の窒素を含有する導電膜をゲート電極3の少なくとも一部として用いる。

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタのチャネル領域に高ストレス窒化膜を用いた場合に比してさらに大きな歪を与えることができる半導体装置を得ること。

【解決手段】シリコン基板10上の所定の位置に形成されるゲート絶縁膜12、ゲート電極13、ゲート絶縁膜12とゲート電極13の積層体の線幅方向両側側面に形成されるオフセットスペーサ膜15、およびオフセットスペーサ膜15の外側に形成されるサイドウォール膜16を有するゲート構造11と、ゲート構造11の線幅方向両側のシリコン基板10表面付近に形成される拡散層17と、を有する電界効果型トランジスタと、サイドウォール膜16と拡散層17上に形成される金属からなるバリア層20と、バリア層20上に形成される金属からなる応力印加層21と、を備え、バリア層20と応力印加層21は、オフセットスペーサ膜15とサイドウォール膜16によってゲート電極13と絶縁されている。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート電極の上方にコンタクトプラグを形成するときに、ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13及びチャネル形成領域12、ゲート電極23、並びに、ゲート絶縁膜30を備えており、ゲート絶縁膜30は、ゲート電極23とチャネル形成領域12との間に形成されたゲート絶縁膜本体部30A、及び、ゲート絶縁膜本体部30Aからゲート電極23の側面部23Aの途中まで延在するゲート絶縁膜延在部30Bから構成されており、チャネル形成領域12の表面を基準としたゲート電極23の高さをHGate、ゲート絶縁膜延在部30Aの高さをHInsとしたとき、HIns<HGateを満足する。

(もっと読む)

半導体装置及びその製造方法

【課題】 シェアードコンタクトがエクステンションに接触することによるジャンクションリークを抑制することができ、且つ面積の増大や抵抗の上昇を招くことなくコンタクトを取る。

【解決手段】 シェアードコンタクトを有する半導体装置において、半導体基板101上にゲート絶縁膜103を介して形成されたゲート電極104と、ゲート電極104の両側面に形成された側壁絶縁膜105,106と、基板101のゲート電極104の両側に隣接する表面部の少なくとも一方が側壁絶縁膜105,106の下部を越えてゲート電極104の下に達するまで除去され、且つ該除去部分に露出するゲート絶縁膜103が除去され、半導体基板101及びゲート絶縁膜103が除去された部分に形成された不純物ドープの半導体層119とを備えた。

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法。

【課題】ゲート電極の上方に層間絶縁層を形成するときに、ゲート電極に対向する基体の部分が酸化されることが無い、絶縁ゲート電界効果トランジスタの製造方法を提供する。

【解決手段】絶縁ゲート電界効果トランジスタの製造方法は、(a)ソース/ドレイン領域13、チャネル形成領域12、チャネル形成領域12上に形成されたゲート絶縁膜30、ソース/ドレイン領域13を覆う絶縁層21、及び、チャネル形成領域12の上方の絶縁層21の部分に設けられたゲート電極形成用開口部22を備えた基体を準備し、(b)ゲート電極形成用開口部22内を導電材料層31,32で埋め込むことでゲート電極23を形成し、次いで、(c)絶縁層21を除去し、その後、(d)全面に、第1の層間絶縁層41、第2の層間絶縁層42を、順次、成膜する工程を備え、前記工程(d)において、酸素原子を含まない成膜雰囲気中で第1の層間絶縁層41を成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に複数の半導体素子を有する半導体装置を少ない工程で簡単に製造する。

【解決手段】アナログ回路素子領域25におけるシリコン酸化膜26の表面への窒素導入と、デジタル回路素子領域24におけるシリコン窒化膜27の形成とを、プラズマ窒化法によって同一の工程で行う。そのため、デジタル回路素子領域24のゲート電極パターンとアナログ回路素子領域25のゲート電極パターンとを、同一のフォトリソグラフィ工程によって形成することが可能になる。したがって、互いに異なる組成を有する2つのゲート絶縁膜上の夫々にゲート電極パターンを形成して成る2つのMOS半導体素子を、少ない工程で簡単に形成することができる。また、工程が少ない分だけ加工精度を高めることができる。

(もっと読む)

半導体装置

【課題】高耐圧で、安全動作領域が広く、かつ、熱散逸性がよく、有効コンダクタンスおよび周波数特性が良好なSOIデバイスを提供すること。

【解決手段】半導体装置100において、p-基板101の表面層の一部にはBOX領域102が設けられる。BOX領域102は、ゲート構造部130の中心から下ろした垂線Lc付近まで設けられており、ドレイン領域112および拡張ドレイン領域108をp-基板101から分離する。ドレイン領域112の厚さは150nm〜300nmのいずれかであり、BOX領域102の厚さは150nm以上である。

(もっと読む)

半導体装置の製造方法

【課題】 ニッケルシリサイドのタングステン含有率を容易に調整可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板1の素子領域1A上にニッケル膜5を形成する工程S1と、シリコン基板1及びニッケル膜5を熱処理し、素子領域1Aの表面をシリサイド化する工程S3と、素子領域1Aの表面をシリサイド化する工程の後に、シリコン基板1上に残留するニッケル膜5を除去する工程S4と、シリコン基板1上に残留するニッケル膜5を除去する工程の後に、6フッ化タングステンガス(WF6)を含む雰囲気中において素子領域1Aの表面を熱処理する工程S6とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】所望のシリサイド組成比を有する金属シリサイド膜からなるフルシリサイド化ゲート電極を精度良く実現する。

【解決手段】第1導電型の第1のMISトランジスタPTrは、第1の活性領域100b上に第1のゲート絶縁膜103bを介して形成され、第1の金属シリサイド膜からなる第1のフルシリサイド化ゲート電極115bを備え、第2導電型の第2のMISトランジスタNTrは、第2の活性領域100a上に第2のゲート絶縁膜105aを介して形成され、第2の金属シリサイド膜からなる第2のフルシリサイド化ゲート電極115aを備え、第2のゲート絶縁膜105aと一体に形成され、素子分離領域101上から第2のフルシリサイド化ゲート電極115aのゲート幅方向の側面上に亘って延設されたL字状絶縁膜105yとを更に備え、第1のフルシリサイド化ゲート電極と第2のフルシリサイド化ゲート電極とは電気的に接続している。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上に、ゲート絶縁膜及びゲート電極を設け、それらの側面にダミー側壁を形成し、その周囲を層間絶縁膜で囲み、前記ゲート電極及びダミー側壁の上面が露出する構造を提供する工程と、

前記ダミー側壁を除去して空洞を形成する工程と、

前記空洞内を側壁材料で埋め、側壁を形成する工程と

を具備する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜上にpMOS電極材料として金属電極を形成する際に金属膜中からゲート絶縁膜へ拡散する炭素成分を抑制し、固定電荷要因を下げることができる半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置の製造方法は、半導体基板100上にゲート絶縁膜101を形成する工程と、ゲート絶縁膜上に薄いシリコン層102を形成する工程と、この薄いシリコン層上にゲート絶縁膜界面での仕事関数が所定範囲内の値となる金属膜103を形成する工程と、を備えたものである。

(もっと読む)

半導体装置

【課題】ソース−ドレイン間の耐圧を確保しつつ、その間隔の微細化を可能にした半導体装置を提供する。

【解決手段】半導体装置は、P型シリコン基板1上に形成したN型エピタキシャルシリコン層5および両者の界面に埋設したN型埋込拡散層3からなる半導体基板と、N型エピタキシャルシリコン層5の主表面SからN型埋込拡散層3に達するトレンチ17と、トレンチ17内の側面を被覆するシリコン酸化膜18と、このシリコン酸化膜18を介してトレンチ17内を埋め込むとともにN型埋込拡散層3に接続する引き出し層19と、同主表面Sに設けたトレンチ9と、このトレンチ9内にシリコン酸化膜10aを介して設けたゲート電極11と、トレンチ9の両側面に設けたN型ソース拡散層13と、同主表面Sにおいてトレンチ17とN型ソース拡散層13との間に設けたトレンチ17aと、このトレンチ17a内に充填したシリコン酸化膜18aと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドの耐熱性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】ゲート領域2、ソース領域4及びドレイン領域5が形成された半導体基板1上にニッケル(またはニッケル合金)6を形成し(図1(A))、第1アニール工程でダイニッケルシリサイド7を形成し(図1(B))、プラズマ処理工程では水素イオンを含有するプラズマにより、水素イオンをダイニッケルシリサイド7またはダイニッケルシリサイド7の下部のゲート領域2、ソース領域4及びドレイン領域5に注入し、第2アニール工程でダイニッケルシリサイド7をニッケルシリサイド8に相変態させる(図1(C))。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】DRAM素子の微細化を進めた場合における、周辺回路側のトランジスタの短チャネル効果を抑制すると共に、コンタクト抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の表面に形成されたMOSトランジスタTr2と、MOSトランジスタTr2のソース108A及びドレイン108Bにそれぞれ接続されるコンタクトプラグ11Aとを具備してなり、コンタクトプラグ11Aが、ソース108A及びドレイン108B上に形成されて不純物が拡散されたエピタキシャル成長層を含んでなることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】導電体プラグと金属シリサイド層との接触面積を容易に確保することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板11上にゲート電極12が形成される。ゲート電極12の側面には、サイドウォール絶縁膜14が形成される。ゲート電極12およびサイドウォール絶縁膜14をマスクとして、半導体基板11に不純物領域15が形成される。不純物領域15の表面に、金属シリサイド層16が形成される。金属シリサイド層16が形成されると、サイドウォール絶縁膜14底面のエッジをゲート電極12側に後退させるエッチングが行われる。当該エッチングが行われた半導体基板11上に、ライナー膜17、および層間絶縁膜18が形成された後、層間絶縁膜18およびライナー膜17にコンタクトホール19が形成される。コンタクトホール19に導電体を充填することで、導電体プラグ20が形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高速動作可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】p型半導体基板11上にゲート絶縁膜21を介して形成されたゲート電極24と、ゲート電極24側面の延長面Aの両側に跨り、半導体基板11内に埋め込まれたp型不純物元素領域33と、p型不純物元素領域33の一部と重畳し、且つゲート電極24端部から外方に延在するn型のソース・ドレイン領域31とを具備している。そして、p型不純物元素領域33とソース・ドレイン領域35との重畳部分における特定深さのp型不純物元素の濃度を、特定深さに対応する重畳部分以外のp型不純物元素領域33部分におけるp型不純物元素の濃度より低くしている。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート構造の半導体装置及びその製造方法の提供を課題とする。

【解決手段】本発明の半導体装置は、半導体基板に形成された溝と、前記溝の内部側にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極の近傍に前記ゲート絶縁膜を介して配置されたソース及びドレインとを具備してなるトレンチゲートトランジスタを備え、該トレンチゲートトランジスタが半導体基板に複数整列形成されてなり、前記トレンチゲートトランジスタが複数整列形成された半導体基板に、前記各トレンチゲートトランジスタの個々の活性領域のみに対応するように前記溝が単独穴型に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】FUSIゲート電極を有し且つソース・ドレイン領域上にシリサイド膜を有する半導体装置において、FUSIゲート電極及びシリサイド膜を制御性よく形成する。

【解決手段】フルシリサイド化された第1のゲート電極117を有する第1のMISトランジスタを備えた半導体装置において、第1のMISトランジスタは、半導体基板100からなる第1の活性領域100aと、第1の活性領域上に形成された第1の金属シリサイド膜からなる第1のゲート電極117と、第1の活性領域における第1のゲート電極117の側方下に位置する領域に形成された第1のソース・ドレイン領域110と、第1のソース・ドレイン領域110上に形成された第1のシリサイド膜119と、第1の活性領域上に、第1のゲート電極117及び第1のシリサイド膜119に接するように形成された下地絶縁膜121と、下地絶縁膜121上に形成された層間絶縁膜122とを備えている。

(もっと読む)

半導体装置

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

201 - 220 / 313

[ Back to top ]