Fターム[5F140BK29]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | PVD (795)

Fターム[5F140BK29]に分類される特許

781 - 795 / 795

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】 チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置とその製造方法を提供すること、及び、MOSトランジスタのチャネルにおけるキャリア分布を直接測定することができる半導体装置の評価方法を提供すること。

【解決手段】 シリコン(半導体)基板10と、シリコン基板10の上に順に形成されたゲート絶縁膜13及びゲート電極14cと、ゲート電極14cの横のシリコン基板10のリセス(穴)10a、10bに形成されたソース/ドレイン材料層18a、18bと、を有し、リセス10a、10bのゲート電極14c寄りの側面10c、10dが、シリコン基板10の少なくとも一つの結晶面で構成されることを特徴とする半導体装置による。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生抵抗を低減して駆動能力を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】 ゲート絶縁膜40を介して形成されたゲート電極50と、ゲート電極側壁55A及び55Bと、半導体基板20の表面部分において、チャネル領域60の両側に、ゲート電極側壁55A及び55Bの下方にそれぞれ形成された第1のソース領域70B及び第1のドレイン領域70Aと、第1のソース領域70Bより接合深さが深い第2のソース領域90B、及び第1のドレイン領域70Aより接合深さが深い第2のドレイン領域90Aと、チャネル領域60の両側にチャネル領域60を挟むように、第1のソース領域70B及び第1のドレイン領域70Aより深い領域まで形成された所定の半導体材料を不純物として含む層80B及び80Aとを備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】静電破壊耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極とドレイン領域とソース領域とを有する半導体装置であって、ドレイン領域は、ゲート電極の第1の側に形成された第1導電型の第1の不純物拡散領域18aと;第1の不純物拡散領域より深く形成された第1導電型の第2の不純物拡散領域20aと;第1の不純物拡散領域より浅く形成され、不純物拡散層より不純物濃度が高い第1導電型の第3の不純物拡散領域28a、28bと;第3の不純物拡散領域上に形成され、ドレインコンタクト部22Dに接続されるシリサイド膜32a、32bとを有し、ドレインコンタクト部とサイドウォール絶縁膜との間にシリサイド膜が形成されていない領域が存在しており、ドレインコンタクト部の下方の半導体基板内に第2の不純物拡散領域が形成されていない。

(もっと読む)

半導体装置及び半導体装置の製造方法

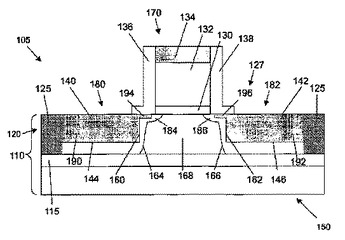

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

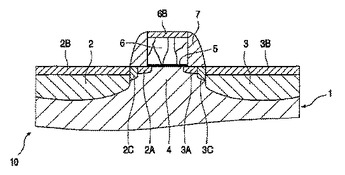

半導体装置とこの種の半導体装置の製造方法

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

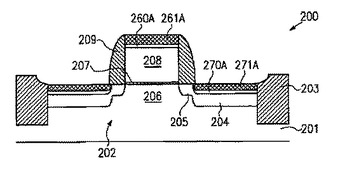

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

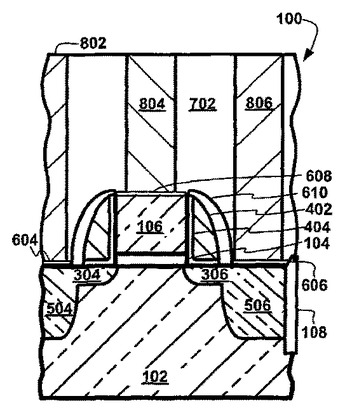

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

781 - 795 / 795

[ Back to top ]