Fターム[5F140CC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 多層 (680)

Fターム[5F140CC01]に分類される特許

661 - 680 / 680

半導体装置及びその製造方法

【課題】サイドウォールの応力によってキャリア移動度を高めることにより、CMOSトランジスタの高速化を図る半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極14a及びPMISトランジスタのゲート電極14bの側面上に、引張応力を有する第1のサイドウォール16a、16bを形成する。その後、基板上の全面に、圧縮応力を有する圧縮応力含有絶縁膜17を形成する。その後、レジスト18をマスクにして、圧縮応力含有絶縁膜17を選択的にエッチングして、ゲート電極14bの側面上に、第2のサイドウォール17aを形成する。その後、第2のサイドウォール17aを覆うレジスト19をマスクにして、圧縮応力含有絶縁膜17を除去する。その後、半導体基板11上の全面に、実質的に応力が生じない層間絶縁膜21を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 MOSトランジスターのきめ細かなマルチVth化により、複雑な信号処理が可能であるアナログ半導体集積回路装置の製造方法を提供する。

【問題解決手段】 MOSトランジスターのソ−スとゲート電極にオーバラップするように選択的に窒化膜を配する製造方法により、かつそのチャネル幅方向の窒化膜のゲート電極へのオーバラップ量をパターン設計値で可変することによりきめ細かなマルチVth化を実現する。

(もっと読む)

トランジスタ、メモリセルアレイ、および、トランジスタ製造方法

【課題】トレンチ型DRAMメモリセルの形成において、垂直型トラジスタとトレンチ型キャパシタの接続を容易化し、高集積化する。

【解決手段】第1および第2ソース/ドレイン領域と、該第1および第2ソース/ドレイン領域を接続する、半導体基板の中に配置されたチャネル領域と、ゲート電極とを含み、該ゲート電極は、上記第1および第2ソース/ドレイン領域間に流れる電流を制御するために、上記チャネル領域に沿って配置され、該チャネル領域から電気的に絶縁されている。また、上記チャネル領域では、該チャネルがリッジ状の形をなしたフィン領域を有している。この「リッジ状」とは、1つの上面と、第1ソース/ドレイン領域と第2ソース/ドレイン領域とを接続する線に対して(断面図では)垂直である2つの側面とからなる。この上面は、半導体基板の表面よりも下に配置されており、ゲート電極は、この上面および2つの側面に沿って設けられる。

(もっと読む)

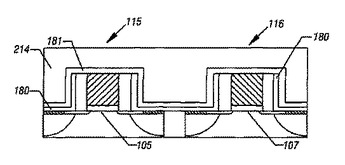

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

窒化珪素膜の製造方法及び半導体装置の製造方法

【課題】 窒化珪素膜の塩素不純物量の低減を実現し、ウェットエッチ耐性の高い窒化珪素膜の形成を可能とした窒化珪素膜の製造方法及びこの製造方法を備えた半導体装置の製造方法を提供することを目的とする。

【解決手段】 基体の表面に窒化珪素膜を形成する窒化珪素膜の製造方法であって、珪素と塩素とを含む第1のガスを前記基体の表面に供給する第1の工程と、窒素を含む第2のガスを前記基体の表面に供給する第2の工程と、水素を含む第3のガスを前記基体の表面に供給する第3の工程と、をこの順に繰り返すことを特徴とする窒化珪素膜の製造方法を提供する。

(もっと読む)

応力制御を伴う窒化シリコン膜

アセンブリは、互いに重ねて形成された窒化物エッチストップ層を有する多層窒化物スタックを備え、これら窒化物エッチストップ層の各々は、膜形成プロセスを使用して形成される。多層窒化物スタックを形成する方法は、単一ウエハ堆積チャンバに基板を配置し、堆積の直前に基板に熱的ショックを与えることを含む。第1の窒化物エッチストップ層が基板上に堆積される。第2の窒化物エッチストップ層が第1の窒化物エッチストップ層上に堆積される。 (もっと読む)

半導体装置及びその製造方法

【課題】電力用のような高耐圧用途に使用できるボディ部分のプロファイルのばらつきの少ないDMOSを提供することを課題とする。

【解決手段】半導体基板の主表面に形成された第一導電型のウェルの所定の領域に形成された第二導電型のDMOSのボディ部分と、半導体基板上に形成されたゲート誘電膜と、ゲート誘電膜上にボディ部分の端部を跨ぐように形成されたゲート電極と、ゲート電極の両側の半導体基板の主表面に形成された第一の導電型の拡散層(但し、拡散層の少なくとも一方がボディ部内に形成されている)と、ボディ部分内に形成されたボディ部分より高い不純物濃度の第二導電型のコンタクト層とを含み、ボディ部分は、深さ方向のボディ部分とウェルとの濃度差が、半導体基板表面におけるボディ部分とウェルとの濃度差より大きい領域を備えていることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程を簡略化することができ、低抵抗のソース、ドレインを具備した高性能かつ高信頼性の薄膜トランジスタを有する半導体装置、その製造方法、薄膜トランジスタアレイ基板及び液晶表示装置を提供する。

【解決手段】 導電型が異なる薄膜トランジスタを含んで構成される半導体装置であって、上記薄膜トランジスタは、基板上に半導体層を形成し、この半導体層上にゲート絶縁膜を介してゲート電極を形成し、ゲート電極をマスクにして半導体層に低濃度の不純物を注入して導電型が異なる低濃度不純物領域をそれぞれ形成し、ゲート電極の側面にサイドウォールスペーサーを形成した後に、ソース、ドレイン領域のみに高濃度不純物層としてSiGeを選択的に形成し、一方の導電型の低濃度不純物領域上のSiGeにのみ高濃度不純物層中の不純物とは異なる他の不純物をドーピングし、低濃度不純物領域上に同じ導電型の高濃度不純物領域を形成したものである半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置およびCMOS集積回路装置

【課題】 nチャネルMOSトランジスタにおいてチャネル領域に大きな圧縮応力を基板面に垂直方向に印加して特性を向上させると同時に、pチャネルMOSトランジスタにおいて、かかる圧縮応力による特性の劣化を軽減する。

【解決手段】 前記ゲート電極を覆うように、応力を蓄積した応力蓄積絶縁膜が形成し、その際、前記応力蓄積絶縁膜のうち、前記ゲート電極を覆う部分の膜厚を、その外側の部分よりも増大させる。

(もっと読む)

半導体装置およびその製造方法

【課題】熱負荷をより小さく抑えて下地への影響なく成膜可能であると共に、十分に引っ張り応力を維持可能でかつパーティクルの発生を抑えた膜質良好な窒化シリコン膜によってMOSトランジスタを覆うことにより、トランジスタ特性の向上を図ることが可能な半導体装置およびこの半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側に形成されたMOSトランジスタ11を覆う状態で窒化シリコン膜13が設けられた半導体装置において、窒化シリコン膜13は、両側の界面層における窒素濃度が中央部分の窒素濃度よりも高いことを特徴としている。窒化シリコン膜の界面層における窒素濃度は、化学量論的組成よりも高いことが好ましい。

(もっと読む)

半導体装置

【課題】 高電圧駆動のMISトランジスタを有する半導体装置であって、耐圧の向上と、微細化の向上が図られた半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体層10と、

前記半導体層10の上方に設けられたゲート絶縁層20と、

前記ゲート絶縁層20の上方に設けられたゲート電極22と、

前記半導体層10に設けられたソース領域またはドレイン領域となる不純物領域28a,bと、

前記ゲート電極22と電気的に接続されたフィールドプレート電極44と、

前記フィールドプレート電極44を覆う絶縁層と、を含み、

前記絶縁層は、比誘電率が異なる領域を有し、比誘電率が高い領域は、前記導電層の一の端部に接している。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

半導体装置

【課題】

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】 チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置とその製造方法を提供すること、及び、MOSトランジスタのチャネルにおけるキャリア分布を直接測定することができる半導体装置の評価方法を提供すること。

【解決手段】 シリコン(半導体)基板10と、シリコン基板10の上に順に形成されたゲート絶縁膜13及びゲート電極14cと、ゲート電極14cの横のシリコン基板10のリセス(穴)10a、10bに形成されたソース/ドレイン材料層18a、18bと、を有し、リセス10a、10bのゲート電極14c寄りの側面10c、10dが、シリコン基板10の少なくとも一つの結晶面で構成されることを特徴とする半導体装置による。

(もっと読む)

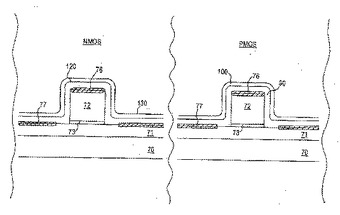

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

pFET中のボロン拡散係数の減少方法

半導体材料の構造物または本体(例えば基板または層)によって定められる境界を横切って加えられる応力を受ける膜は、境界の近傍の半導体材料中に引張り応力から圧縮応力への変化を提供し、アニーリングの間のホウ素拡散速度を変化させ、ひいては最終ホウ素濃度またはプロフィル/勾配あるいはその両方を変化させるために用いられる。電界効果トランジスターの場合、側壁の有無にかかわらず、ソース/ドレイン、拡張注入部またはハロ注入部、あるいはその両方に対する境界の位置を調節するために、ゲート構造物を形成させることができる。水平方向と垂直方向とで異なるホウ素拡散速度を作り出すことができ、ヒ素と同程度の拡散速度を実現することができる。同じプロセス工程で、nFETとpFETとの両方の接合キャパシタンスの減少を同時に実現することができる。

(もっと読む)

(もっと読む)

半導体装置および半導体集積回路装置

pチャネルMOSトランジスタおよびnチャネルMOSトランジスタの各々においてチャネル方向を<100>方向に設定し、STI型素子分離構造に、引っ張り応力を蓄積した第1の応力補償膜を形成し、さらにシリコン基板上に素子分離構造を覆うように引っ張り応力を蓄積した第2の応力補償膜を形成する。 (もっと読む)

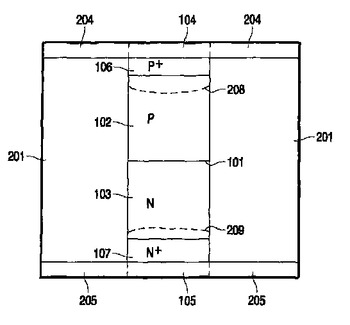

高絶縁破壊電圧を有する半導体装置

半導体装置、例えば、pn接合(101)を有するダイオード(200)がこのpn接合の近傍に、そして、これを跨ぐこともある絶縁材料の電界形成領域(201)を有する。電界形成領域(201)は好ましくは高誘電率を有し、容量性電圧結合領域(204,205)を介してpn接合に印加されるのとほぼ同じ電圧に結合される。pn接合(101)間に逆電圧が印加され且つ装置が非道通時に、電界形成領域(201)が存在しない場合に存在しうるpn接合空乏領域の限界を超えて延びる電界形成領域の一部分に容量性電界が存在し、電界形成領域内の電界が拡張された電界を誘起し、この拡張された電界は対応して拡張されたpn接合空乏領域(208,209)までとされ、装置の逆絶縁破壊電圧を増加させる。  (もっと読む)

(もっと読む)

661 - 680 / 680

[ Back to top ]