Fターム[5F140CE18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 局所的アニール (144)

Fターム[5F140CE18]に分類される特許

81 - 100 / 144

半導体装置の製造方法

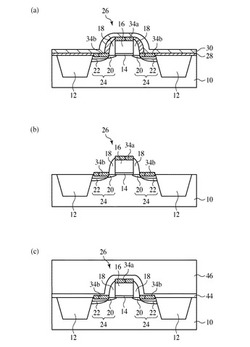

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

応力印加チャネル領域を有する電界効果トランジスタを備えた半導体構造の形成方法

半導体構造の製造方法は、第1トランジスタ素子および第2トランジスタ素子を有する半導体基板を提供するステップを有する。前記第1トランジスタ素子は少なくとも1つの第1アモルファス領域を含み、前記第2トランジスタ素子は少なくとも1つの第2アモルファス領域を含む。前記第1トランジスタ素子の上に応力発生層が形成される。前記応力発生層は、前記第2トランジスタ素子は覆わない。第1アニールプロセスが実施される。前記第1アニールプロセスは、前記第1アモルファス領域および前記第2アモルファス領域を再結晶化させるために適合されている。前記第1アニールプロセス後に、第2アニールプロセスが実施される。前記第2アニールプロセス中は、前記応力発生層が前記基板上に残されている。  (もっと読む)

(もっと読む)

固体撮像素子及びその製造方法、並びに半導体装置及びその製造方法

【課題】p型不純物領域の活性化を低温で行うことを可能にする固体撮像素子の製造方法を提供する。

【解決手段】光電変換が行われる受光センサ部が半導体基体内に形成され、この半導体基体の表面側に配線層又は電極層が形成され、半導体基体に、表面側とは反対の裏面側から光を入射させる裏面照射型構造を有する固体撮像素子を製造する際に、半導体基体の裏面側の部分をアモルファス化してアモルファス半導体層62を形成する工程と、半導体基体の裏面側へp型不純物をイオン注入63する工程とを、それぞれ行い、その後に、レーザーアニール65によってp型不純物を活性化させることにより、半導体基体の裏面側にp型半導体領域31を形成する。

(もっと読む)

アニール装置、アニール方法及び半導体装置の製造方法

【課題】基板上の半導体装置における素子の電気的特性を概ね同じに揃える。

【解決手段】加熱部12と記憶部16と演算部17と制御部15とを具備するアニール装置を用いる。加熱部12は、複数の領域を有し、複数の領域の各々ごとにアニール温度の調整が可能である。記憶部16は、加熱対象の素子の形状的な特徴を示す形状パラメータとアニール温度と加熱対象の素子の電気的特性とを関連付けた実績データを記憶する。演算部17は、複数の領域の各々ごとに、基板上の製造中の当該領域に対応する素子の形状パラメータに基づいて、記憶部16を参照して、所望の電気的特性を得られるアニール温度)を決定する。制御部15は、記複数の領域の各々ごとに、決定されたアニール温度で当該領域に対応する素子を加熱するように加熱部12を制御する。

(もっと読む)

フィン構造体及びこれを利用したフィントランジスタの製造方法

【課題】フィン構造体及びこれを適用したフィントランジスタの製造方法を提供する。

【解決手段】側面を持つメサ構造体を基板に複数形成した後、この上に半導体層を形成するフィン構造体の製造方法を提供する。半導体層上にはキャッピング層が形成され、したがって、半導体層は、キャッピング層により保護され、フィン構造体で製造される部分を持つ。キャッピング層は、平坦化によりその上部が一部除去され、これを通じてメサ構造体の上面に位置する半導体層が除去され、したがって、メサ構造体の側面に相互隔離されたフィン構造体が形成される。これにより、非常に狭い幅のフィン構造体を形成でき、フィン構造体の厚さ及び位置の制御が非常に容易になる。

(もっと読む)

半導体装置及びその製造方法

【課題】 トランジスタのドレイン電流がその表面に形成された絶縁膜の応力によって変化することを利用して、ウェハ面内におけるドレイン電流バラツキの抑制された半導体装置を提供する。

【解決手段】 MOS型トランジスタ素子上に応力調整用絶縁膜10を有し、MOS型トランジスタ素子のゲート線幅Lgの設計値からの変動量に応じて、応力調整用絶縁膜10の応力が紫外線11の照射により調整されている。MOS型トランジスタ素子がP型MOSFETの場合は、同じ設計値に対してゲート線幅が小さいほど応力が大きくなるように調整され、MOS型トランジスタ素子がN型MOSFETの場合は、同じ設計値に対してゲート線幅が大きいほど応力が大きくなるように調整されている。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート絶縁膜のリーク電流の増加を抑制することができる半導体装置を得ること。

【解決手段】シリコン基板1上にSiON膜12−1aを形成する工程と、SiON膜12−1a上にハフニウムと酸素とが結合したハフニウムオキサイドを含むハフニウムオキサイド膜12−2aを形成する工程と、ハフニウムオキサイド膜12−2a中にハフニウムをイオン注入する工程と、ハフニウムをイオン注入したハフニウムオキサイド膜12−2aをアニール処理して活性化させる工程と、ハフニウムオキサイド膜12−2a上にゲート電極となるPt膜を形成する工程と、Pt膜、ハフニウムオキサイド膜12−2a、SiON膜12−1aを所定の形状にパターニングする工程と、を含む。

(もっと読む)

最先端CMOSデバイスの接触抵抗を減少する方法

本発明において、半導体デバイスの接触抵抗を減少する方法が提供される。一実施形態では、この方法は、ソース及びドレイン領域並びにゲート構造を有する半導体デバイスが形成された基板を準備するステップと、熱アニールプロセスにより基板上でケイ化プロセスを遂行するステップと、基板上でレーザーアニールプロセスを遂行するステップと、を備えている。別の実施形態では、この方法は、注入されたドーパントを有する基板を準備するステップと、熱アニールプロセスにより基板上でケイ化プロセスを遂行するステップと、レーザーアニールプロセスによってドーパントを活性化するステップと、を備えている。 (もっと読む)

半導体装置の製造方法

【課題】所望の仕事関数を有するフルシリサイドゲート電極を形成する。

【解決手段】半導体基板上にゲート絶縁膜を介してポリシリコンを形成して(ステップS1)、ボロンやヒ素等の不純物をイオン注入した後(ステップS2)、そのポリシリコンにレーザを照射する(ステップS3)。このレーザ照射後のポリシリコンをフルシリサイド化し(ステップS4)、フルシリサイドゲート電極を形成する。イオン注入後のレーザ照射により、不純物を固溶限界の制限を受けずにゲート電極材料内に分布させることが可能になるため、導入した不純物の量に応じた仕事関数を有するフルシリサイドゲート電極を形成することが可能になる。

(もっと読む)

半導体装置及びその製造方法

【課題】p型及びn型のMOSFETのいずれにおいても、仕事関数が制御されていることにより、閾値電圧が低減され且つ制御されたCMOSトランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置100は、半導体基板101と、半導体基板101におけるn型MOSFET領域の上に形成された第1のゲート電極131と、半導体基板101におけるp型MOSFET領域の上に形成された第2のゲート電極132とを備え、第1のゲート電極131は、シリコン層107及びその上に形成された第1の金属シリサイド層118を含み、第2のゲート電極132は、金属過剰な第2の金属シリサイド層119を含む。

(もっと読む)

半導体装置の製造方法

【課題】超高速昇降温アニールによるスリップ転位や脆性破壊に対するウェハ強度を確保できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、バルク内部の酸素析出物密度が5×106〜5×107cm−3で、そのサイズが100nmより小さく、且つ溶存酸素濃度が1.1×1018〜1.2×1018cm−3のSi基板の主表面に不純物をイオン注入する工程と、前記Si基板に昇降温速度が1×105℃/secより高い超高速昇降温アニールを施し、前記不純物を電気的に活性化して半導体素子の少なくとも一部を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのゲート電極、ソース領域およびドレイン領域にニッケルシリサイド膜を形成した場合に、このニッケルシリサイド膜の高抵抗化および凝集を抑制できる一方で、層間絶縁膜中に含まれる水素や水分を充分に除去できる技術を提供する。

【解決手段】MISFETのゲート電極6a、6b、ソース領域およびドレイン領域にニッケルシリサイド膜16を形成する。その後、半導体基板1上に窒化シリコン膜17を形成する。続いて、半導体基板1に対してスパイクアニールを実施する。スパイクアニールは、例えば、レーザアニール装置を用いて行ない、温度を700℃以上1300℃以下にし、かつ、加熱時間を1マイクロ秒以上1ミリ秒以下にする条件で実施する。

(もっと読む)

半導体装置の製造方法

【課題】 高温で長時間の活性化熱処理を行うことなく、パターンエッジ部周辺に発生す

る応力を軽減することにより高濃度不純物領域の活性化熱処理で発生する転位の拡張を抑

制する。

【解決手段】 LDD構造を有するMOSトランジスタのソース・ドレイン領域の形成に

おいて、P型シリコン基板101上にゲート絶縁膜102を介して、ゲート電極103を

形成後、ゲート電極103等をイオン注入マスクとして、イオン注入を行い、さらに熱処

理によって、n−低濃度不純物領域106を形成する。さらにゲート電極に隣接するゲー

ト電極側壁104を形成する。このゲート電極側壁104等をイオン注入マスクとして、

n+高濃度不純物領域107をイオン注入で形成し、ソース・ドレイン領域108を形成

する。

さらに第1のゲート電極側壁104に隣接して、第2のゲート電極側壁105を形成す

る。その後、ソース・ドレイン領域108の活性化熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】高性能の高誘電率ゲート絶縁膜を安価に製造することができる、半導体装置の製造方法を提供する。

【解決手段】半導体基板101に、pウェル103およびnウェル104を形成し、半導体基板101の表面に高誘電率膜105aおよびシリコン膜105bを形成し、さらに、これらの膜を1000〜1050℃でアニールする。そして、高誘電率膜105aおよびシリコン膜105bをパターニングして、高誘電率ゲート絶縁膜106,107およびゲート電極108,109を形成し、エクステンション領域111,114、サイドウォール110,113、高濃度不純物領域112,115等を形成する。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長層からなるエクステンション部を有し、かつ、ゲート長の短い半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体基板1上に、第1ゲート22を形成する工程と、少なくとも第1ゲート22の表面を窒化処理して、第1ゲートを保護する窒化膜24を形成する工程と、窒化処理において半導体基板1上に形成された窒化膜24を選択的に除去する工程と、第1ゲート22の両側における半導体基板1上に、エピタキシャル成長層を形成する工程とを有する。

(もっと読む)

基板に形成された熱処理構造用の方法および装置

本発明は概して、基板の所望の領域にアニーリングプロセスを実行するために使用される1つ以上の装置および種々の方法について説明している。一実施形態では、多量のエネルギーが該基板の表面に送出されて、該基板のある所望の領域を優先的に溶解して、事前の処理ステップから作成された不要なダメージを除去して、該基板の種々の領域においてドーパントをより均等に分布させて、および/または該基板の種々の領域を活性化させる。該優先的溶解プロセスは、該基板の該溶解領域における該ドーパント原子の拡散レートおよび溶解度の増大ゆえに、該溶解領域における該ドーパントのより均一な分布を可能にする。従って溶解領域の作成は、1)ドーパント原子をより均一に再分布させること、2)事前処理ステップで作成された欠陥が除去されること、および3)極めて急激なドーパント濃度を有する領域が形成されることを可能にする。 (もっと読む)

半導体装置及びその製造方法

【課題】ソース・ドレイン領域及びゲート電極を高不純物密度化し、且つゲートリーク電流を抑制した半導体装置及びその製造方法を提供する。

【解決手段】第1導電型の半導体領域2と、半導体領域2の一部を挟んだ第2導電型のソース領域9a及びドレイン領域9bと、ソース領域9aと半導体領域2との間のソース領域9aより浅い第2導電型のソースエクステンション領域11aと、ドレイン領域9bと半導体領域2との間のドレイン領域9bより浅い第2導電型のドレインエクステンション領域11bと、半導体領域2の上の第1ゲート絶縁膜71nと、この第1ゲート絶縁膜71nの上の窒素濃度20〜57%の第2ゲート絶縁膜72nと、この第2ゲート絶縁膜72nの上の第2導電型の半導体多結晶膜からなるゲート電極77nとを備える。

(もっと読む)

半導体装置の製造方法

【課題】Siウェハ中にダメージを発生させないフラッシュランプアニール法を実現すること。

【解決手段】半導体装置の製造方法は、単結晶Si領域を含むSiウェハであって、前記単結晶Si領域上に長手方向が前記単結晶Si領域の結晶方位と異なるラインパターンを含むパターンが設けられた前記Siウェハの上方に、光源としてフラッシュランプ光源またはライン状のビームを出射するレーザーを配置する工程と、前記光源から放射された光により前記Siウェハを加熱する工程であって、前記光により前記Siウェハ上に形成される光強度分布が、前記単結晶Si体領域の結晶方位とは異なる方向において強度が最大値となる分布が形成されるように、前記Siウェハを加熱する工程とを有し、前記単結晶Si領域の前記結晶方位が、前記単結晶Si領域の劈開面の面方位であることを特徴とする。

(もっと読む)

不純物ドーピング領域を含む半導体素子及びその形成方法

【課題】高集積化に最適化された、不純物ドーピング領域を含む半導体素子及びその形成方法を提供する。

【解決手段】この方法は、半導体基板にクラスタ型ドーパントイオンを注入して不純物注入領域を形成する段階(S200)と、前記不純物注入領域にレーザアニーリング工程を実行して不純物ドーピング領域を形成する段階(S210)とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】応力制御膜に生ずる複数の歪によって異なる複数種のトランジスタのチャネル移動度を向上させる。

【解決手段】シリコン基板21上にn型FET素子領域30aとp型FET素子領域30bとを形成し、ゲート電極25a,25bおよびソース・ドレイン領域28a,28bを内包すると共に、p型FET素子領域30bに対して最適化された真性応力を有する応力制御膜31を形成し、n型FET素子領域30a上の応力制御膜31に対して化学反応処理を施すことによって、n型FET素子領域30a上に他とは異なる真性応力を有する応力制御膜31aにす。こうして、互いに異なる応力を両FET素子領域30a,30bに作用させてチャネル領域の電子移動度を向上させ、ドレイン電流を向上させる。

(もっと読む)

81 - 100 / 144

[ Back to top ]