Fターム[5F140CE18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 局所的アニール (144)

Fターム[5F140CE18]に分類される特許

121 - 140 / 144

半導体装置の製造方法および半導体装置

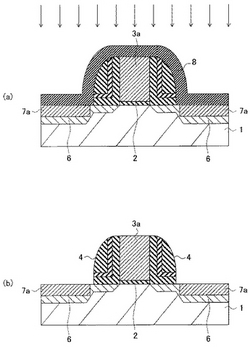

【課題】ゲート電極を全て合金化(フルシリサイド化)させる一方で、ソース・ドレイン領域においては合金化反応を抑制することができ、接合リークの発生を抑制することができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2を介してゲート電極を形成した後、ゲート電極の側壁にサイドウォール絶縁膜4を形成する。ゲート電極およびサイドウォール絶縁膜4をマスクとしたイオン注入により、ソース・ドレイン領域6を形成する。その後、ゲート電極を被覆するように半導体基板1上に高融点金属膜8を堆積させ、アニール処理を行う。本発明では、アニール処理において、ゲート電極材料のバンドギャップよりも大きいエネルギーをもつ電磁波を照射する。これにより、フルシリサイド化したゲート電極3aが形成され、ソース・ドレイン領域6中には浅いシリサイド層7aが形成される。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 電界効果型トランジスタの短チャネル効果を効果的に抑制しつつ、製造安定性を向上させる。

【解決手段】 シリコン基板101に、第一導電型の第一不純物と反対導電型のハロー不純物をイオン注入した後、第一導電型の第一不純物をイオン注入し、第一不純物が注入された領域に、シリコン基板101を溶融させない条件でレーザ光を照射することにより、p型ハロー領域113およびn型エクステンション領域111を形成する。その後、第一導電型の第二不純物をシリコン基板101にイオン注入し、第二不純物が注入された領域に、シリコン基板101を溶融させない条件でレーザ光を照射することにより、n型ソース・ドレイン領域109を形成する。

(もっと読む)

半導体装置及びその製造方法

半導体基板(101)上にゲート絶縁膜(102)を介して形成されたゲート電極(103)に不純物を導入し、ゲート電極(103)に対してレーザ光照射を行って、導入した不純物をゲート電極(103)のゲート絶縁膜(102)との界面まで拡散させるようにして、ゲート電極(103)の空乏化を抑制する。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果によるリーク電流の低減に優れた半導体装置およびその製造方法を提供する。

【解決手段】単結晶半導体基板上に形成された電界効果トランジスタの作成過程において、エクステンション領域を形成するために不純物を導入するとともに、単結晶格子を崩してアモルファス化させる。または、不純物および原子量の大きい元素を導入することによって、単結晶格子を崩してアモルファス化させる。そして、パルス幅が1fs以上10ps以下、かつ波長が370nm以上640nm以下のレーザビームを照射することにより、アモルファス化した部分のみを選択的に活性化させ、エクステンション領域を20nm以下の厚さで形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】 RTAによるアニール法は、微細化に限界がある。RTAによるアニール法は、加熱時間が数秒で、半導体基板全体が高温に加熱されるために不純物が半導体基板の深部へ拡散する恐れがあるため、今後のさらなる微細化に対応することが困難である。

【解決手段】レーザ光を非線形光学素子に通すことなく基本波のままとし、高強度、且つ、繰り返し周波数の高いパルスのレーザ光を不純物拡散層に照射してレーザアニールを行って不純物を電気的に活性化させることを特徴とする。本発明により、シリコン基板表面の薄い層を局所的に溶かして活性化することができる。また、一度のレーザ走査で活性化される領域の幅を拡大することができるため、格段に生産性を向上させることができる。

(もっと読む)

深く炭素がドーピングされた領域並びに隆起したドナーがドーピングされたソース及びドレインを特徴とする歪みnMOSトランジスタ

本発明に係る複数の実施例は、炭素がドーピングされた領域、及び隆起したソース/ドレイン領域を有することで、nMOSトランジスタチャネル中に引っ張り応力を供する。

(もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

半導体基板及びその製造方法

【課題】小さい寄生容量及び高いキャリヤ移動度を有する半導体基板を提供する。

【解決手段】Si基板10と、Si基板10上に形成された所定幅のSiO2層12と、両側にそれぞれ第1の端部40a及び第2の端部40bを有し、第1の端部40a及び第2の端部40bから側方向のエピタキシャル成長によって形成され、SiO2層12を覆うSiGe層40と、SiO2層12に対応してSiGe層40上にエピタキシャル成長によって形成され、Siの格子変形が誘導されたストレインSi層50と、を備える半導体基板である。

(もっと読む)

ヘテロ集積型歪みシリコンn型MOSFET及びp型MOSFET及びその製造方法

【課題】 n型及びp型MOSFETデバイスに使用するための半導体構造体と、その製造方法とを提供する。

【解決手段】 半導体構造体は、n型MOSFETが製造されるウェハ領域の層構造が、p型MOSFETが製造されるウェハ領域の層構造とは異なるものとなるように製造される。この構造体は、まず、Heなどの軽原子のイオン注入によりSi含有基板の表面に損傷領域を形成することによって、製造される。次いで、損傷領域を含むSi含有基板の上に、歪みSiGe合金が形成される。次いで、アニール・ステップを使用し、欠陥に起因する歪み緩和によって歪みSiGe合金を実質的に緩和させる。次に、緩和したSiGe合金の上に、歪みSiなどの歪み半導体キャップが形成される。

(もっと読む)

レーザ・アニールによる固相エピタキシャル成長(epitaxy)再結晶化

MOS型トランジスタの浅く急峻な傾斜ドレイン拡張部を製造するための方法(70)を説明する。この方法では、半導体製品の製造におけるレーザSPERアニール・プロセスを用いて、ドレイン拡張部内で固相エピタキシャル成長再結晶化が成される。一つの方法(70)は、基板のチャネル領域に隣接する基板の拡張領域内深くにゲルマニウムなどの重イオン種を打ち込んで深い非晶化領域を形成し、その後、チャネル領域に隣接する基板の拡張領域内にボロン又は別のこのようなドーパント種を打ち込む、事前非晶化プロセス(74)を含む。打ち込んだドーパントを、その後、低温でプレアニール(78)して接合深さ及びドーピング濃度を定める。その後、拡張部及び/又は深いソース/ドレイン領域を、チャネル領域に近接する領域の固相エピタキシャル成長再結晶化を提供する高温のレーザでアニールして(84)、急峻な傾斜を有する超高ドーピング濃度及び活性化レベルを達成する。  (もっと読む)

(もっと読む)

ドープされたチタン酸ボディを有するMOS(Metal−Oxide−Semiconductor)デバイス

単結晶のチタン酸ストロンチウム又はチタン酸バリウム(10)のボディを有するMOS(Metal-Oxide-Semiconductor)デバイスが提供され、ボディは、絶縁領域に隣接するドープされた半導体領域(24)を備えている。ボディは、絶縁領域により、半導体領域から分離した、ドープされた導通領域を、さらに備えていてもよい。様々な手法でドープされた場合の単結晶チタン酸ストロンチウムの材料特性は、MOSスタックの絶縁構成部、導通構成部、及び、半導体構成部を提供するために、用いられる。有利なことに、単一のボディを用いることにより、スタック構成部の間のインターフェースレイヤの存在を回避することができ、電界効果トランジスタなどのMOSデバイスの特性を改善する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】導通時における駆動力を向上させる。

【解決手段】所定の開口を有するマスク層を用いて、基板1とドレイン領域2からなる半導体基体の一主面側に所定の溝15を形成する工程と、少なくとも溝15の側壁に接して、該溝15からはみ出すように埋め込み領域11を形成する工程と、半導体基体並びに埋め込み領域11に接するようにヘテロ半導体層30を形成する工程と、ヘテロ半導体層30をパターニングし、ヘテロ半導体領域3を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】 Coシリサイド電極をもつ半導体装置の製造プロセスを簡素化し、Coシリサイド膜及びキャップ層の厚さを制御可能とすることでコンタクトホールに於けるアスペクト比の減少を実現し、Coシリサイド膜を形成する際の未反応Coからなる残渣の発生を皆無にすると共にCo酸化物を容易に除去して清浄を維持できるようにする。

【解決手段】 Si基板21上にCo及びSiを同時に蒸着するか或いはCoを堆積した後に加熱するCoシリサイド膜22の形成に於いて、カルボキシル基をもつガス状物質に曝露しながら、或いは、曝露した後に加熱し、表面に在るCo及びSiのうち、Coはカルボン酸塩として揮発させると共にSiは酸化してSiO2 からなる保護膜であるキャップ層25とする工程が含まれてなることを基本とする。

(もっと読む)

半導体装置の製造方法

【課題】 短波長光の照射による活性化により、浅接合の拡散層を形成する際の、ゲート絶縁膜中のトラップの発生を抑える。

【解決手段】 半導体装置の製造において、まず、基板に、ゲート絶縁膜を介して、ゲート電極を形成する。少なくともゲート電極をマスクとして、不純物を注入し、拡散層を形成する。また、この拡散層形成のための不純物注入の前又は後に、少なくともゲート電極をマスクとして、フッ素イオンを注入する。更に、波長約1000nm以下の光を、約1ミリ秒以内の時間照射する。

(もっと読む)

極浅接合の形成方法

【課題】 極浅接合を形成する方法を提供する。

【解決手段】 p型素子に極浅接合を形成する方法は、アルミニウムイオンをn型にドープされたシリコンに打ち込み、続いてアルミニウムを活性化させ、かつ拡散させるために低温アニーリングを行う。アルミニウムを使用することによりホウ素を使用した場合に比べ、より浅い接合を形成することができる、抵抗が低くなる、より低温でのアニーリングが可能となるといった様々な利点が生まれる。

(もっと読む)

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 高温での熱処理に耐性のない層の形成後に不純物の活性化を行う。

【解決手段】 半導体基板中の不純物領域の活性化を波長1.1μm以下の領域に主たるスペクトラムのピークをもつ電磁波の照射で行うようにした。このような電磁波では、従来のWハロゲンランプのような赤外光を中心とした電磁波での熱処理と比べ、シリコン基板内での吸収係数が高く、基板のごく一部の活性化したい領域のみを局所的に加熱することができるため、熱に耐性のない非耐高熱性材料を用いた領域を400°C以下に保つことができる。したがって、例えば、半導体基板上に金属層または金属合金層や層間絶縁膜を形成した後に活性化を行ったり、半導体基板に接着性塗布膜及び支持基板を張り合わせる工程の後に活性化を行うことも可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 不純物のプロファイルを精度よく制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体領域1に不純物元素のイオンを注入する工程と、半導体領域に、所定元素としてIV族の元素又は不純物元素と同一導電型であって不純物元素よりも質量数が大きい元素のイオンを注入してアモルファス状態の結晶欠陥領域5を形成する工程と、不純物元素及び所定元素が注入された領域にフラッシュランプの光を照射してアニールを行い、アモルファス状態の結晶欠陥領域の結晶欠陥を回復させるとともに不純物元素を活性化する工程と、を備え、フラッシュランプの光を照射してアニールを行う工程を、結晶欠陥領域のアモルファス状態が維持される温度で半導体領域を予め加熱した状態で行う。

(もっと読む)

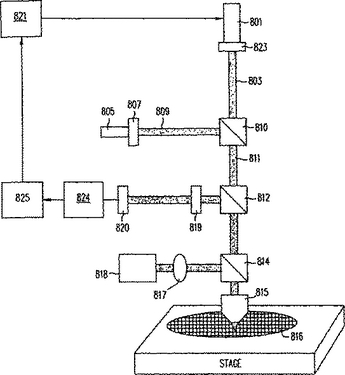

拡散層の横方向拡散の測定

ウェーハ加工プロセスにおける更なるステップとして、ドーピングされた層の横方向急峻性を監視するために、どのような半導体ウェーハ加工プロセスをも変更することができる。一実施形態においては、1つ以上のドーピングされた領域を含むテスト構造が、製品ウェーハに形成され(例えば、1つ以上のトランジスタと同時に)、テスト構造の1つ以上の寸法が測定され、ウェーハのその他のドーピング領域における、例えば、同時に形成されたトランジスタにおける横方向急峻性の判断として使用される。テスト構造におけるドーピングされる領域は、お互いに一定の間隔を置いて規則正しく配置することができ、あるいは、隣接するドーピングされた領域間の間隔を変化させて配置されてもよい。あるいは、または、それに加えて、複数のテスト構造が、単一ウェーハに形成されてもよく、それぞれのテスト構造においては、ドーピングされた領域は、一定の空間的間隔で配置され、異なるテスト構造は、異なる空間的間隔を有する。  (もっと読む)

(もっと読む)

121 - 140 / 144

[ Back to top ]