Fターム[5F140CE18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 局所的アニール (144)

Fターム[5F140CE18]に分類される特許

141 - 144 / 144

注入され計数されたドーパントイオン

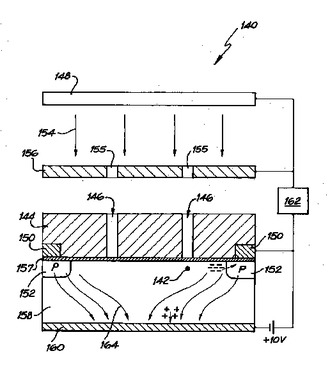

本発明は、実質的に真性な半導体の基板(158)の領域に注入された、計数された数のドーパントイオン(142)を有する汎用タイプの半導体装置に関する。基板(158)の一つ以上のドープされた表面領域は、金属化され、電極(150)が形成される。計数された数のドーパントイオン(142)が、実質的に真性な半導体の領域に注入される。

【その他】

原文には、請求項11及び請求項11Aが存在する。請求項11Aは、オンライン手続上、請求項11内に記載した。

(もっと読む)

(もっと読む)

半導体製造用のゲート電極ドーパント活性化方法

一実施形態において、本発明は、一般に、基板上に堆積されたドープされた層をアニールするための方法を提供する。この方法は、ゲート酸化物層のような基板の表面に多結晶層を堆積するステップと、この多結晶層にドーパントを注入して、ドープされた多結晶層を形成するステップとを備えている。この方法は、更に、ドープされた多結晶層を急速加熱アニールに露出して、多結晶層全体にわたりドーパントを容易に分配するステップを備えている。その後、この方法は、ドープされた多結晶層をレーザアニールに露出して、多結晶層の上部のドーパントを活性化するステップを備えている。レーザアニールは、ドーパント、即ち原子を多結晶材料の結晶格子へ合体させる。 (もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

多成分誘電体膜を形成するためのシステム及び方法

【課題】半導体用途における誘電体膜を形成するためのシステム及び方法、特に、混合気化前駆体を用いて基板上に多成分誘電体膜を作製するためのシステム及び方法を提供する。

【解決手段】本発明は、気化した前駆体の混合物が、原子層堆積(ALD)処理における単一パルス段階中にチャンバ内に一緒に存在して多成分膜を形成するような気化前駆体の混合をもたらすためのシステム及び方法を提供する。気化前駆体は、少なくとも1つの異なる化学成分から成り、そのような異なる成分が単層を形成して多成分膜を生成することになる。本発明の更に別の態様では、組成勾配を有する誘電体膜が提供される。

(もっと読む)

141 - 144 / 144

[ Back to top ]