Fターム[5F140CE18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 局所的アニール (144)

Fターム[5F140CE18]に分類される特許

21 - 40 / 144

NMOSエピ層の形成方法

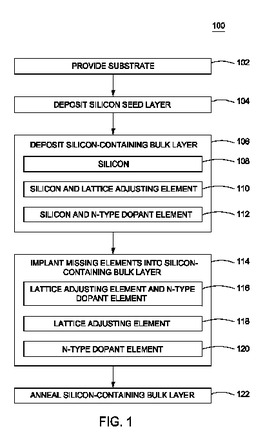

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

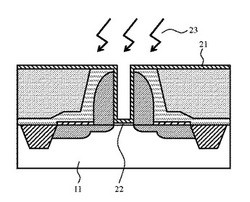

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 所望の極浅拡散層を形成することが可能な半導体製造方法を提供する。

【解決手段】

シリコン基板1にイオン注入するイオン注入工程と、イオン注入工程の後に、シリコン

基板1にマイクロ波を照射するマイクロ波照射工程と、マイクロ波照射工程の後に、シリ

コン基板1を熱処理装置に移し、シリコン基板に0.1ミリ以上100m秒以下のパルス

幅の光を照射することにより、シリコン基板1を熱処理する熱処理工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】混晶層に発生する転位、結晶欠陥を抑制することができる半導体装置を提供すること。

【解決手段】p型のSi基板13表面のn型ウェル層16の両端に形成され、SiおよびGeからなる混晶層18と、これらの混晶層18の表面にそれぞれ形成されたp型の不純物注入層19、20と、これらの不純物注入層19、20をそれぞれドレイン領域、ソース領域とするpMOSFET15−1と、を具備する素子領域11と、この素子領域11を囲うようにSi基板13の表面に形成された素子分離層14−1と、この素子分離層14−1外のSi基板13の表面に前記素子領域11の混晶層18と同一材料で形成され、その主方向が、Si基板13の<110>方向とは異なるダミーパターン35と、を具備する。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置の製造方法

【課題】より高温の活性化FLAを行ってもウェハが割れることなく、SDエクステンション抵抗を下げることができる半導体装置の製造方法を提供する。

【解決手段】ウェハをウェハ表面温度1100℃以上に0.1〜10ミリ秒で加熱するための高強度のフラッシュランプアニールを照射する際、その直前のウェハ表面温度を800〜1000℃と高温にする。ウェハの予備加熱を、波形を調整したフラッシュで行うことにより不純物の拡散を抑制する。この手法により、アモルファス層を形成していないウェハ表面を効果的に活性化できるため、欠陥が少なく、かつ浅く低抵抗な接合が形成できる。

(もっと読む)

半導体装置の製造方法

【課題】不純物を活性化するときにミリ秒アニールを用いても、電圧ストレスに起因した閾値電圧のシフト量が大きくなることを抑制する。

【解決手段】半導体基板100上に、酸化シリコンより誘電率が高い高誘電率膜134を含むゲート絶縁膜130を形成する。ゲート絶縁膜130上に、金属膜を含むゲート電極140を形成する。半導体基板100に不純物を導入することにより、エクステンション領域170を形成する。エクステンション領域170に光を照射することにより、エクステンション領域170が1000℃以上となる時間を100ミリ秒以下にした第1の熱処理を行う。ついで、半導体基板100に700℃以上900℃以下の第2の熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面を均一にアニールする半導体装置の製造方法を提供する。

【解決手段】半導体基板に第1不純物元素を注入する工程と、前記半導体基板上に絶縁膜となる酸化膜または窒化膜を形成する膜成膜工程と、前記絶縁膜上にシリコン膜を形成するシリコン膜成膜工程と、前記シリコン膜に第2不純物元素を注入する注入工程と、前記第2不純物元素が注入された前記シリコン膜にシリコンの吸収端の波長よりも短い波長の光を照射する短波長光アニール工程と、前記短波長光アニール工程の後、前記シリコン膜にシリコンの吸収端の波長よりも長い波長の光を照射する長波長光アニール工程と、を有する半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体素子とその製造方法、及び電子機器

【課題】素子基板の剛性を確保することと、ゲート絶縁膜に効率良く水素を供給することを、両立させることができる技術を提供する。

【解決手段】本発明の半導体素子の製造方法は、素子基板2の第1面側にトランジスタ3とこれに電気的につながる配線層12,16を形成する工程と、素子基板2の第1面と反対側の第2面に複数の孔21を形成する工程と、それらの孔21を通して素子基板2の第2面からトランジスタ3のゲート絶縁膜5に水素を供給する工程とを有する。

(もっと読む)

歪誘起合金及び段階的なドーパントプロファイルを含むその場で形成されるドレイン及びソース領域

【解決手段】

トランジスタのドーパントプロファイルは、その場で(in situ)ドープされた歪誘起半導体合金に基いて得ることができ、段階的なドーパント濃度が高さ方向に沿って確立され得る。その結果、半導体合金をチャネル領域にごく近接して位置させることができ、それにより全体的な歪誘起効果を高めることができる一方で、最終的に得られるドーパントプロファイルについて過度に妥協しなくてよい。更に、半導体合金を選択的に成長させるのに先立ち追加的な注入種が組み込まれてよく、それにより内部歪の注入誘起緩和を回避することができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の空乏化と、ゲート電極内の不純物量の減少ないしはバラつきと、イオンがゲート絶縁膜を突き抜けてしまうことに起因したゲート絶縁膜の信頼性低下及び閾値変動を抑制する。

【解決手段】第1注入工程(図1(b)、図1(c))と第2注入工程(図1(d)、図1(e))を備える。第1注入工程ではゲート絶縁膜5と、ゲート電極9、10となる膜6と、が形成された半導体基板1のゲート電極9、10となる部分に、n型又はp型の導電型のイオンを注入する。第2注入工程では、ゲート電極9、10に同じ導電型のイオンを注入する。第1注入工程で注入するイオンの質量は、第2注入工程で注入するイオンよりも大きくする。これにより第1注入工程による不純物の濃度分布の縦方向におけるピーク位置を、第2注入工程による不純物のピーク位置よりもゲート絶縁膜5寄りにする。

(もっと読む)

半導体装置およびその製造方法

【課題】 エッチング処理を行わなくても、基底面内転位を有する半導体層から結晶成長された半導体層に基底面内転位が伝播することを防止することができる技術を提供する。

【解決手段】 本発明の方法は、半導体層2の表面2aにおける基底面内転位6の位置8を特定する特定工程と、特定工程で特定された位置8において結晶の再配列を行う結晶再配列工程と、結晶再配列工程の後に表面2aから半導体層を結晶成長させる結晶成長工程とを備えている。本発明によると、結晶成長された半導体層に基底面内転位6が伝播しない。基底面内転位6が結晶成長された半導体層に伝播していないために、リーク電流を抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜形成工程のような大きな熱負荷を避けて、チャネルの最上面の不純物濃度を薄くした、深さ方向のドーピング・プロファイルを実現し、オン電流が向上する半導体装置の製造方法を提供することである。

【解決手段】 ゲート電極形成後にゲート電極をマスクにして角度10度以下でチャネル不純物をイオン注入し、この後、チャネル不純物の活性化を、基板表面から所定の深さのチャネル不純物濃度がゲート長方向に一定になるように、RTAを用いたアニールで行う、さらに、その後のエクステンション/ハロー注入、深いS/D注入の後の活性化を、拡散レスアニールで行う。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化し、サーマルバジェットの小さなアニールプロセスを用いてトランジスタを作製しても、リーク電流の増大を抑制できる半導体装置を提供すること。

【解決手段】第1導電型の半導体基板上に絶縁膜を介してゲート電極を有し、前記ゲート電極とは絶縁された形で、前記ゲート電極の直下の前記半導体基板のチャネル領域の両側に、第2導電型の不純物がドーピングされたソース・ドレイン領域を有し、前記ソース・ドレイン領域と前記チャネル領域の間に、前記ソース・ドレイン領域と同じ第2導電型であり、前記ソース・ドレイン領域よりも浅く、前記ソース・ドレイン領域と繋がったエクステンション領域を有し、前記エクステンション領域の近傍の第1導電型の領域に、周囲の領域よりも格子欠陥密度の高い高密度欠陥領域が局所的に形成され、前記高密度欠陥領域には、点欠陥が集合した点欠陥集合体が含まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスにおいてフォトレジスト構造等の追加工程を必要としない、非対称なDSS構造の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の側面に形成されたオフセットスペーサ13、23と、一方のオフセットスペーサ23の側面に形成されたゲート側壁27と、半導体基板2中のゲート絶縁膜21下に形成されたチャネル領域25と、半導体基板2内のチャネル領域25を挟む領域に形成され、チャネル領域25側に導電型不純物が偏析して形成されたエクステンション領域24aを有するソース・ドレイン領域24と、ソース・ドレイン領域24上にオフセットスペーサ13に接して形成されたシリサイド層16、及び、ゲート側壁27に接して形成されたシリサイド層26と、を有した半導体装置1とする。

(もっと読む)

薄膜形成方法、及び薄膜形成装置

【課題】 低温で形成されたSiO2膜は高温で形成されたSiO2膜より特性が僅かに劣るため、そのままでは使う事が出来なかった。又、高温で形成されたSiO2膜と同等の特性を得るためには、後工程で少なくとも500℃以上でのアニールを行う必要があった。ところが、プロセス低温化の要求から、基板温度を500℃以下に維持したまま、高品質なSiO2膜を形成する技術の開発が必要とされていた。

【解決手段】

活性な酸素原子を用いて500℃以下の低温でSiO2膜を成膜後、紫外光をシリコン基板のシリコン酸化膜側表面に1回または複数回照射する事で、Si基板を高温にする事なくSiO2膜の特性を改善させる事が可能となった。前記紫外光とは、200nm以上370nm以下の波長のみが含まれ、1回の照射時間が0.1マイクロ秒以下であり、照射1回当たりのエネルギー密度が0.01J/cm2以上であるという条件を満たす紫外光である。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

21 - 40 / 144

[ Back to top ]