Fターム[5F152CD14]の内容

再結晶化技術 (53,633) | 被結晶化層の下方の層 (4,095) | 材料(結晶化直前の状態) (3,330) | 絶縁体 (2,749) | SiN (830)

Fターム[5F152CD14]に分類される特許

201 - 220 / 830

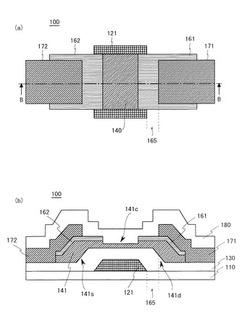

薄膜トランジスタ、その製造方法および表示装置

【課題】大きなオン電流を維持したままオフ電流を低減するとともに、製造が容易なLDD領域を備える薄膜トランジスタを提供する。

【解決手段】平面視において、ドレイン電極171をゲート電極121から所定の距離だけ離して形成することによって、LDD領域165となるオーミックコンタクト層161を水平方向に形成する。この場合、LDD領域165は、ゲート電極121の電位に基づく電界の影響を受けにくくなり、実質的にドレイン電極171の電位に基づく電界による電界集中のみを緩和する。したがって、TFT100は、結晶性シリコン膜からなるチャネル領域141cを形成することにより、大きなオン電流を維持することができると同時に、オフ電流を十分低減することができる。

(もっと読む)

薄膜トランジスタ、その製造方法、半導体装置および表示装置

【課題】オン電流が大きく、かつ電気的特性のばらつきが小さな薄膜トランジスタおよびその製造方法を提供する。

【解決手段】周辺TFT110のチャネル層141を形成するシリコンの結晶粒径は、微結晶シリコンによって形成されているので、閾値電圧のばらつきをある程度抑えながら、オン電流を大きくすることができる。しかし、多結晶シリコンからなるチャネル層を有する周辺TFTと比べて、小さなオン電流しか流すことができない。そこで、周辺TFT110のゲート電極125と対向する窒化シリコン膜180の表面に、さらにゲート電極195を形成する。この結果、チャネル層341を流れるオン電流は、2つのゲート電極125、195によって制御されるので、オン電流の不足分を補うことができる。

(もっと読む)

平板表示装置及びその製造方法

【課題】平板表示装置及びその製造方法を提供する。

【解決手段】基板と、TFT活性層と、キャパシタの第1下部電極及び第1下部電極上に形成されたキャパシタの第1上部電極と、第1絶縁層と、チャンネル領域に対応する領域に順次に形成されたゲート下部電極及びゲート上部電極と、キャパシタの第1上部電極に対応する領域に順次に形成されたキャパシタの第2下部電極及び上部電極と、画素下部電極及び画素下部電極を露出させるように画素下部電極エッジの上部に配された画素上部電極と、活性層のソース及びドレイン領域を露出させるコンタクトホール、及び画素上部電極エッジの一部を露出させるビアホールによって貫通される第2絶縁層と、第2絶縁層上に形成され、コンタクトホール及びビアホールを通じて、ソース、ドレイン領域及び画素上部電極と接続するソース及びドレイン電極と、を備える平板表示装置。

(もっと読む)

薄膜トランジスタ、多結晶酸化物半導体薄膜の製造方法、及び薄膜トランジスタの製造方法

【課題】InとGaとZnからなる群のうち少なくとも1つの元素を含有する酸化物半導体からなる薄膜が、高いTFT特性を有することが可能な薄膜トランジスタ、多結晶酸化物半導体薄膜の製造方法、及び薄膜トランジスタの製造方法を提供する。

【解決手段】第1工程として、基板12上に、IGZO系の組成を有する多結晶焼結体をターゲットとした気相成膜法を用いて、InとGaとZnからなる群のうち少なくとも1つの元素を含有する非晶質酸化物半導体からなる薄膜10Aを成膜する。第2工程として、非晶質酸化物半導体からなる薄膜10Aを、電気炉へ投入し、その表面粗さRa値を1.5nm以下として維持しつつ多結晶化する温度領域660℃〜840℃で焼成する。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】レーザー光の照射による単結晶半導体層の端部からの膜剥がれを抑制した、SOI基板の作製方法及び半導体装置の作製方法を提供する。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、絶縁層を介して単結晶半導体基板とベース基板とを貼り合わせ、脆化領域において単結晶半導体基板を分離してベース基板上に絶縁層を介して単結晶半導体層を形成し、単結晶半導体層の端部を除去し、端部を除去した単結晶半導体層の表面にレーザー光を照射する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジスタを配置する。

(もっと読む)

SOI基板の作製方法、半導体装置の作製方法

【課題】SOI基板の単結晶半導体層中の酸素濃度を低減させる方法を提供する。

【解決手段】単結晶半導体層を溶融状態にすることによって酸素の外方拡散を促進する。具体的には、ベース基板上に設けられた酸素を含有する接合層と、前記酸素を含有する接合層上に設けられた単結晶半導体層と、を有するSOI構造を形成し、前記ベース基板の温度を500℃以上の温度であって前記ベース基板の融点よりも低い温度に加熱した状態において、前記単結晶半導体層をレーザー光の照射により部分溶融させることによって、SOI基板を作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】工程を簡単にしながらも、多結晶化された半導体層の厚みの変動を低減する。

【解決手段】半導体装置1は、基板11の平坦な表面に形成された遮光膜14と、遮光膜14を直接に覆って基板11に形成されると共に、平坦化された表面を有する平坦層15と、遮光膜14に重なるように平坦層15上に形成され、多結晶化された半導体層16とを備えている。

(もっと読む)

バックチャネルエッチ型の薄膜トランジスタ、半導体装置、及びこれらの製造方法

【課題】生産性及びトランジスタ特性を向上することができるバックチャネルエッチ型の薄膜トランジスタ、半導体装置、及びこれらの製造方法を提供することを目的とする。

【解決手段】本発明にかかるバックチャネルエッチ型のTFT108は、ゲート電極11と、ゲート電極11上に形成されたSiN膜12と、SiN膜12上にパターニング形成されたSiO膜13とを有する。さらに、TFT108は、SiO膜13上においてSiO膜13に接し、全てのパターン端がSiO膜13のパターン端近傍に配置されるようにパターニング形成された多結晶半導体膜14を有する。

(もっと読む)

薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置する第1半導体層及び第2半導体層と、前記第1半導体層及び第2半導体層と絶縁されるゲート電極と、前記第1半導体層及び第2半導体層と前記ゲート電極とを絶縁するゲート絶縁膜と、前記ゲート電極と絶縁され、前記第2半導体層と一部が接続するソース/ドレインである電極とを含み、前記第1半導体層は前記第2半導体層の下部に位置し、前記第1半導体層の面積は第2半導体層の面積よりも小さいことを特徴とする薄膜トランジスタ及びその製造方法に関する。また、前記薄膜トランジスタを含む有機電界発光表示装置とその製造方法に関する。

(もっと読む)

多結晶シリコンの製造方法、薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置する第1の半導体層及び第2の半導体層と、前記第1の半導体層及び第2の半導体層と絶縁されているゲート電極と、前記第1の半導体層及び第2の半導体層と前記ゲート電極とを絶縁するゲート絶縁膜と、前記ゲート電極と絶縁され、前記第2の半導体層に一部が接続するソース/ドレイン電極とを含み、前記第1の半導体層上部に前記第2の半導体層が位置することを特徴とする薄膜トランジスタ及びその製造方法に関する。

(もっと読む)

半導体薄膜の改質方法、改質した半導体薄膜とその評価方法、およびこの半導体薄膜で形成した薄膜トランジスタ、並びにこの薄膜トランジスタを用いて構成した回路を有する画像表示装置

【課題】多結晶半導体をレーザアニール法によって形成する方法に於いて、多結晶半導体膜の表面ラフネスを低減する。

【解決手段】レーザアニール装置の光学系に非晶質シリコン半導体薄膜を成膜した基板1の走査方向における照射光強度分布を、高エネルギの光強度側の微結晶しきい値以上のエネルギ領域と表層のみ融合するエネルギ領域を有する分布として制御する透過率分布フィルタ6を設置し、通常のラインビームを利用するエキシマレーザアニール法または位相シフトストライプマスク法またはSLS法に適用する事によって、それぞれの方法で得られる多結晶の表面突起の高さを低減する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体デバイスに用いるのに好適な酸化物半導体の提供を目的の一とする。又は、それを用いた半導体装置の提供を目的の一とする。

【解決手段】In−Ga−Zn−O系酸化物半導体層をトランジスタのチャネル形成領域に用いた半導体装置であって、In−Ga−Zn−O系酸化物半導体層は、InGaO3(ZnO)m(m>0)で表される非晶質構造中に、InGaO3(ZnO)m(m=1)で表される結晶粒を含む構造を有する。

(もっと読む)

表示装置、電子機器および表示装置の製造方法

【課題】トランジスタの役割に応じて能動層を構成する結晶シリコン層の結晶粒の粒径を

異ならせることが可能な表示装置を提供する。

【解決手段】このEL装置100(表示装置)は、金属層21および基板1の表面上に形

成されるバッファ膜22および23と、金属層21が形成されない領域上のバッファ膜2

3の表面上に形成される能動層24を有する画素選択用トランジスタ7と、金属層21が

形成される領域上のバッファ膜23の表面上に形成される能動層25を有する駆動電流制

御用トランジスタ8とを備え、駆動電流制御用トランジスタ8の能動層25を構成する結

晶シリコン層50(結晶シリコン領域50b)の結晶粒の平均粒径は、画素選択用トラン

ジスタ7の能動層24を構成する結晶シリコン層50(結晶シリコン領域50a)の結晶

粒の平均粒径よりも小さい。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタアレイ基板、及び表示装置

【課題】優れたオン電流特性と、優れたオフ電流特性を兼ね備え、かつ歩留まりの向上が可能な薄膜トランジスタを提供する。

【解決手段】本発明に係る薄膜トランジスタは、下層半導体層11と、上層半導体層12の間には、ソース領域10S/ドレイン領域10Dに開口部を有する絶縁膜4が形成され、開口部H1,H2を介して、下層半導体層11と上層半導体層12が接続される。下層半導体層11のうち、少なくともソース領域10S/ドレイン領域10Dの間に配置されるチャネル領域10C、及び開口部H1,H2と対向する領域のうちの前記チャネル領域から延設される少なくとも一部の領域は、多結晶半導体層であり、上層半導体層は、非晶質半導体層である。

(もっと読む)

SOI基板の作製方法

【課題】撓みやすい基板をベース基板として用いる場合であっても、半導体層が設けられた基板(ベース基板)を歩留まりよく作製する。

【解決手段】半導体層が設けられた基板の作製方法において、基板上に設けられた半導体層にレーザ光を照射して当該半導体層の表面を平坦化する工程を有することを特徴とする。そして、前記半導体層の表面を平坦化する工程において、前記レーザ光の照射により前記半導体層が完全溶融するのに必要な最小の照射エネルギー密度を100%としたとき、前記半導体層に照射する前記レーザ光の照射エネルギー密度を72%以上98%以下とし、好ましくは85%以上96%以下とする。

(もっと読む)

有機電界発光表示装置及びその製造方法

【課題】有機電界発光表示装置及びその製造方法を提供する。

【解決手段】画素領域と非画素領域を備える基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置し、チャネル領域及びソース/ドレイン領域を備える半導体層と、前記半導体層のチャネル領域に対応するように位置するゲート電極と、前記半導体層と前記ゲート電極とを絶縁させるゲート絶縁膜と、前記半導体層のソース/ドレイン領域に電気的に接続するソース/ドレイン電極と、前記ゲート電極と前記ソース/ドレイン電極とを絶縁させる層間絶縁膜とを含み、前記バッファ層、ゲート絶縁膜、及び層間絶縁膜は、非画素領域上の一部が除去された形態で位置し、前記除去された面積はパネル面積の8〜40%であることを特徴とする有機電界発光表示装置の製造方法に関する。

(もっと読む)

半導体装置の作製方法

【課題】面方位が(100)の単結晶シリコン膜および面方位が(110)の単結晶シリコン膜を有するSOI基板を、高い歩留まりで作製する方法を提供する。

【解決手段】面方位が(100)の第1の単結晶シリコン基板1000内に第1のイオンをドープして、第1の脆化層を形成する。面方位が(110)の第2の単結晶シリコン基板1002内に第2のイオンをドープして選択的に第2の脆化層を形成する。第1の加熱処理では、第1の脆化層のみから第1の単結晶シリコン基板の一部をはく離し、第1の単結晶シリコン膜を形成する。第2の単結晶シリコン基板であって、第2の脆化層が形成されていない領域を除去し、第2の加熱処理では、第2の脆化層から第2の単結晶シリコン基板の一部をはく離し、第2の単結晶シリコン膜を形成する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】小粒径の多結晶シリコン層と、大粒径の多結晶シリコン層を同時に作る手法として、シリコン層の堆積時に小粒径の多結晶シリコン層を形成し、所望の領域のみにCWレーザーを照射し大粒径化する技術が知られている。しかし、この技術を用いる場合、小粒径の多結晶シリコン層中に不対電子を埋める水素を残しての処理が必要となり、製造工程にかかる時間が長くなるという課題がある。

【解決手段】一部に金属層311がある基板310上に窒化珪素層312を形成し、窒化珪素層312上に、酸化珪素層313を形成し、パルスレーザーを照射する。酸化珪素層313の層厚により小粒径の多結晶シリコン層と大粒径の多結晶シリコン層とが入れ替わるように形成されるため、小粒径の多結晶シリコン層と、大粒径の多結晶シリコン層を同時に形成することが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の作製工程において、高調波のCWレーザを半導体膜上に相対的に走査させながら照射すると、走査方向に延びた長い結晶粒がいくつも形成される。このようにして形成された半導体膜は前記走査方向においては実質的に単結晶に近い特性のものとなるが、高調波のCWレーザの出力が小さくアニールの効率が悪い。

【解決手段】第2高調波に変換されたCWレーザと同時に基本波のCWレーザを半導体膜の同一部分に照射することで、出力の補助を行う。通常、基本波は1μmあたりの波長域に入り、この波長域では半導体膜に対する吸収が低い。しかしながら、可視光線以下の高調波を基本波と同時に半導体膜に照射すると、高調波により溶かされた半導体膜に基本波はよく吸収されるため、アニールの効率が著しく上がる。

(もっと読む)

201 - 220 / 830

[ Back to top ]