Fターム[5F152CD25]の内容

再結晶化技術 (53,633) | 被結晶化層の下方の層 (4,095) | 形状(結晶化直前の状態) (465) | 孔、溝 (70)

Fターム[5F152CD25]の下位に属するFターム

微小孔、微小溝(径200nm以下) (27)

Fターム[5F152CD25]に分類される特許

1 - 20 / 43

結晶化シリコン層の製造方法、半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置

【課題】金属原子が内部に拡散、侵入せず、かつ、結晶化方位や粒径を制御することのできる結晶化シリコン層の製造方法、かかる方法を利用した半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置を提供すること。

【解決手段】結晶化シリコン層を形成するにあたって、基板本体10d上に金属触媒層8および第1非結晶シリコン層4xを形成した後、熱処理を行ない、第1非結晶シリコン層4xと金属触媒層8との間での相互拡散により、第1非結晶シリコン層4xと金属触媒層8とを入れ替える。その際、第1非結晶シリコン層4xは、多結晶シリコン層4yに変化する。金属触媒層8を除去した後、開口部15aを備えた絶縁層15、および第2非結晶シリコン層1xを形成した状態で熱処理を行ない、第2非結晶シリコン層1xを、開口部15aの底部で多結晶シリコン層4yと接している部分を起点にして結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】短時間且つ低温で高品質な多結晶シリコンを形成する方法を提供する。

【解決手段】微結晶11aを含むアモルファス半導体膜11にマイクロ波を用いたアニールを行うことで、微結晶11aを核として微結晶11aを含むアモルファス半導体膜11を結晶化する。

(もっと読む)

半導体装置の製造方法

【課題】格子定数が異なる複数種類の半導体素子やスピン機能素子を同一の基板上の同一の層上に混載することが可能な半導体装置の製造方法を提供しようとする。

【解決手段】シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜に開口部を設け、前記シリコン基板の一部を露出させる工程と、前記露出したシリコン基板及び前記絶縁膜上にGeを含むアモルファスの第1の半導体層を形成する工程と、前記第1の半導体層を第1の方向に延伸した構造に加工する工程と、前記第1の方向に延伸した第1の半導体層に熱処理を加えて、前記開口部から離れるにしたがってSiの濃度が減少する第1のSi1-xGex(0≦x≦1)層を形成する工程と、を含む。

(もっと読む)

酸化物半導体膜、および半導体装置

【課題】半導体装置に用いるのに好適な新たな構造の酸化物半導体膜を提供することを目的の一とする。または、新たな構造の酸化物半導体膜を用いた半導体装置を提供することを目的の一とする。

【解決手段】非晶質を主たる構成とする非晶質領域と、表面近傍の、In2Ga2ZnO7の結晶粒を含む結晶領域と、を有し、結晶粒は、そのc軸が、表面に対して略垂直な方向となるように配向している酸化物半導体膜である。または、このような酸化物半導体膜を用いた半導体装置である。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】トランジスタを有する半導体装置であって、絶縁表面上に所定の間隔を隔てて互いに平行に配列された複数の短冊状の半導体膜と、前記複数の短冊状の半導体膜の上面及び側面に接するゲート絶縁膜と、前記ゲート絶縁膜を介して前記複数の短冊状の半導体膜の上面及び側面を覆うゲート電極を有する半導体装置である。半導体膜の上部及び側部をチャネル形成領域とすることで、電流駆動能力を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】 固相エピタキシャル成長によって、所望の面方位を有する結晶を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、第1の面方位を有するシリコン基板11上の一部に、アモルファス層13を形成する工程と、そのアモルファス層13にマイクロ波を照射し、前記アモルファス層13を第1の面方位を有する結晶層とする工程とを有していることを特徴とする半導体装置の製造方法を提供することができる。

(もっと読む)

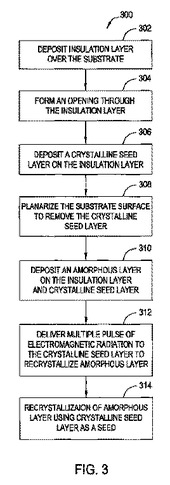

パルストレインアニール法を使用する薄膜の固相再結晶化の方法

本発明の実施形態は、電磁エネルギーの複数のパルスを使用する薄膜の固相再結晶化の方法を提供する。一実施形態では、アモルファス層が、再結晶化すると下の結晶性のシード領域またはシード層と同じグレイン構造および結晶配向を有するように堆積されている、結晶性のシード領域またはシード層へ複数のエネルギーのパルスを供給することによって、基板表面全体または基板の表面の選択された領域をアニールするために本発明の方法を使用することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 単結晶構造の柱状構造を有する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に単結晶の柱状構造を形成する方法であって、前記半導体基板上に絶縁膜を形成する工程と、前記絶縁膜に溝を形成し、前記溝の底部に少なくとも前記半導体基板の一部を露出させる工程と、前記溝内部に少なくともゲルマニウムを含む埋め込み膜を形成する工程と、熱処理により前記埋め込み膜を溶融させる工程と、溶融した前記埋め込み膜を、前記半導体基板をシードとして単結晶化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

多結晶シリコン薄膜の製造方法

多結晶シリコン薄膜の製造方法は、絶縁基板の上に金属層を形成する金属層形成段階と、前記金属層形成段階で形成された金属層の上にシリコン層を積層する第1シリコン層形成段階と、触媒金属原子が金属層から前記シリコン層に移動してシリサイド層を形成するように熱処理を行う第1熱処理段階と、前記シリサイド層の上に非晶質シリコン層を積層させる第2シリコン層形成段階と、前記シリサイド層の粒子を媒介として、非晶質シリコン層から結晶質シリコンが生成されるように熱処理を行う結晶化段階と、を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が低い半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板と、埋め込み酸化膜と、第2導電型の半導体層と、を備えるSOI基板に作られ、前記埋め込み酸化膜は、自己に穿設された、前記半導体基板と前記半導体層とを連通する、第1の開口を有し、前記半導体基板は、その表面部分に埋め込み状態に形成され、前記第1の開口内の前記半導体層の埋設部と互いに電気的に接続している、第2導電型の接続層を有し、前記半導体層及び前記埋め込み酸化膜を貫通して、前記接続層の表面部分に至る第2の開口内に埋め込まれて、側面において前記半導体層と電気的に接続し、底面において前記接続層と電気的に接続する、コンタクト電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、結晶化触媒の均一な低濃度拡散制御で金属触媒から形成されるシードの位置を調整して多結晶シリコーン層内のチャネル領域を単結晶に近いように形成することによって薄膜トランジスタの素子特性を向上させて均一な値を得ることができる薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタは基板上に形成された金属触媒層、金属触媒層上に次々と形成された第1キャッピング層及び第2キャッピング層パターンを含む。製造方法は金属触媒層上に第1キャッピング層を形成する。第1キャッピング層上に第2キャッピング層を形成してパターニングする。パターニングされた第2キャッピング層上に非晶質シリコーン層を形成する。金属触媒を拡散させる。非晶質シリコーン層を結晶化して多結晶シリコーン層を形成する段階を含む。

(もっと読む)

半導体基板、半導体基板の製造方法、トランジスタ、並びに電気光学装置

【課題】多結晶シリコンを(111)配向を選択的に形成する場合、結晶粒界の位置はランダムに形成されるため、トランジスタのチャネル部分に結晶粒が配置された場合、結晶粒界に存在するトラップ準位の影響により、電気的特性が低下する。また、チャネル部分に発生したホットキャリアを吸収する領域がなく、キンク特性が発生するという課題がある。

【解決手段】(111)配向を含む不純物がドーピングされた第1シリコン層204上に貫通孔206を含む絶縁層205を形成した後、第2シリコン層前駆体207aを積層し、XeClエキシマレーザを用いて第1シリコン層204を種結晶として再結晶工程を行い、面方位が(111)に揃えられた第2シリコン層207を形成する。そして不純物がドーピングされた第1シリコン層204からホットキャリアを引き抜くことで、キンクの発生が抑えられ、且つ電気的特性に優れたトランジスタを提供できる。

(もっと読む)

レーザ加工方法及び半導体装置

【課題】 帯状の絶縁パターンの中央近傍に結晶粒界が発生することを防止することが可能なレーザ加工方法を提供する。

【解決手段】 単結晶半導体基板と、その半導体基板よりも熱伝導率の低い材料からなり、相互に平行に配置されて前記半導体基板まで達する複数の溝が形成されている第1の膜と、アモルファスまたはマイクロクリスタルの半導体からなり、溝内及び第1の膜の上に配置されている第2の膜とを有する加工対象物を準備する。第2の膜に、第2の膜の表面において溝の長手方向と平行な長尺ビームであるパルスレーザビームを入射させ、パルスレーザビームの入射位置を、第2の膜の表面において、溝の長手方向と交差する方向に、オーバラップさせながら移動させる。第2の膜の表面におけるパルスレーザビームのビームプロファイルの短軸方向の幅が、相互に隣り合う溝の間隔よりも狭い。

(もっと読む)

半導体装置及びその製造方法

【課題】 SOI構造の埋め込み絶縁膜の開口部における基板シリコンのダメージを防止すると共に、埋め込み絶縁膜の開口部における基板との接触面積の低下を防止する。

【解決手段】 SOI構造を有する半導体装置において、シリコン基板10と、シリコン基板10上に設けられ、一部に開口部12を有し、該開口部12の上部を上面側が広がった順テーパー構造に形成し、且つ下部を下面側が広がった逆テーパー構造に形成した絶縁膜11と、絶縁膜11上及び開口部12内に形成された単結晶シリコン層14と、単結晶シリコン層14に形成された半導体素子とを備えた。

(もっと読む)

1 - 20 / 43

[ Back to top ]