Fターム[5F152LL09]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | PVD (427) | MBE、CBE (255)

Fターム[5F152LL09]に分類される特許

1 - 20 / 255

半導体発光素子、半導体発光素子の製造方法および発光装置

III族窒化物半導体デバイスの製造方法

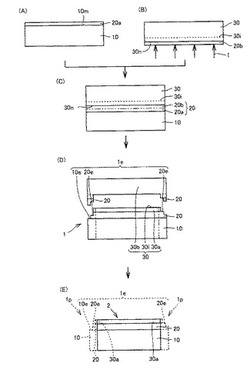

III族窒化物複合基板の製造方法

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

シリコン単結晶膜およびその製造方法

【課題】薄層化された自立性のシリコン単結晶膜を提供し、また、剥離時の熱処理温度を格段に低減することができる新たなシリコン単結晶膜の形成方法を提供する。

【解決手段】シリコン単結晶膜6は、Siの含有率が、90原子%以上であり、厚みが、50μm以下であり、自立性がある。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度であり第1下側層よりも高い濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

スイッチング素子

【課題】逆ピエゾ効果が効果的に抑制され、オフ時の高電界状態であっても、ゲート電極近傍でクラックの発生が抑止されたスイッチング素子を提供する。

【解決手段】スイッチング素子1は、電子走行層13と、電子走行層13の上面に形成され、バンドギャップが電子走行層13より大きく電子走行層13とヘテロ接合する電子供給層14と、ソース電極15とドレイン電極16と、ソース電極15とドレイン電極16の間に配置されたゲート電極17とを備え、ゲート電極の下方に、電子供給層14に替えて、逆ピエゾ抑制層20を配置してなる。逆ピエゾ抑制層20は、ヘテロ接合よりも格子不整合が緩和された状態で電子走行層13と接合するように、その組成等が調整されており、ゲート電極17との接触領域A2のドレイン電極16側境界B4を跨ぐように配置される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

β−Ga2O3系単結晶膜の製造方法

【課題】ホモエピタキシャル成長法を用いて伝導特性に優れたβ−Ga2O3単結晶膜を形成することができるβ−Ga2O3単結晶膜の製造方法を提供する。

【解決手段】分子線エピタキシー法により、Snを添加しながらβ−Ga2O3結晶をβ−Ga2O3基板2上、又は前記β−Ga2O3基板上に形成されたβ−Ga2O3系結晶層上にホモエピタキシャル成長させ、Sn添加β−Ga2O3結晶膜を形成する工程と、第1の不活性雰囲気中で前記Sn添加β−Ga2O3結晶膜に第1のアニール処理を施す工程とを含む方法により、Sn添加β−Ga2O3単結晶膜を製造する。

(もっと読む)

複合基板およびその製造方法、ならびに複合ウエハ

【課題】III族窒化物とは化学組成の異なる異組成基板とIII族窒化物層とが貼り合わされた複合基板であっても、反りおよびクラックを発生させることなくその複合基板上にIII族窒化物エピタキシャル層を形成することができる複合基板およびその製造方法を提供する。

【解決手段】本複合基板2Dは、III族窒化物以外の化学組成を有する異組成基板10と、異組成基板10に貼り合わされたIII族窒化物層21と、含み、III族窒化物層21は、平面充填が可能な少なくとも1種類の平面形状を有する複数のIII族窒化物タイル21pに分離している。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

半導体ウエハの製造方法、複合基体および複合基板

【課題】半導体デバイスを効率よく製造するために、基体の種類の如何を問わずに効率よく半導体ウエハを製造することができる半導体ウエハの製造方法、ならびにかかる製造方法に好適に用いられる複合基体および複合基板を提供する。

【解決手段】本半導体ウエハの製造方法は、基体10上に、表面のRMS粗さが10nm以下の基体表面平坦化層12を形成して複合基体1を得る工程と、複合基体1の基体表面平坦化層12側に半導体結晶層20aを貼り合わせて複合基板3A,3B,3Cを得る工程と、複合基板3A,3B,3Cの半導体結晶層20a上に少なくとも1層の半導体層30を成長させる工程と、基体表面平坦化層12をウェットエッチングで除去することにより、基体10から半導体結晶層20aを分離して、半導体結晶層20aおよび半導体層30を含む半導体ウエハ5を得る工程と、を含む。

(もっと読む)

半導体装置

【課題】シリコンなどの基板上に形成した高品質な結晶を有する半導体装置を提供する。

【解決手段】実施形態によれば、GaNを含む下地層と、窒化物半導体を含む機能部と、前記下地層と前記機能部との間に設けられ、AlNを含む層を含む中間層と、を備えた半導体装置が提供される。前記下地層のうちの前記中間層とは反対側の第1領域におけるシリコン原子の濃度は、前記下地層のうちの前記中間層の側の第2領域におけるシリコン原子の濃度よりも高く、前記下地層の前記中間層とは反対側の第1面は、複数の凹部を有する。

(もっと読む)

1 - 20 / 255

[ Back to top ]