Fターム[5F152LM05]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 選択成長 (201) | 横方向成長するもの(Lateral Overgrowth) (40)

Fターム[5F152LM05]に分類される特許

1 - 20 / 40

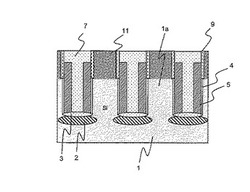

半導体装置の製造方法

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

半導体装置

【課題】シリコンなどの基板上に形成した高品質な結晶を有する半導体装置を提供する。

【解決手段】実施形態によれば、GaNを含む下地層と、窒化物半導体を含む機能部と、前記下地層と前記機能部との間に設けられ、AlNを含む層を含む中間層と、を備えた半導体装置が提供される。前記下地層のうちの前記中間層とは反対側の第1領域におけるシリコン原子の濃度は、前記下地層のうちの前記中間層の側の第2領域におけるシリコン原子の濃度よりも高く、前記下地層の前記中間層とは反対側の第1面は、複数の凹部を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

炭化珪素基板を有する複合基板

【課題】複合基板が有する複数の炭化珪素基板の間の隙間への異物の残留を防ぐことができる複合基板を提供する。

【解決手段】第1の炭化珪素基板11は、支持部30に接合された第1の裏面B1と、第1の裏面B1に対向する第1の表面T1と、第1の裏面B1および第1の表面T1をつなぐ第1の側面S1とを有する。第2の炭化珪素基板12は、支持部30に接合された第2の裏面B2と、第2の裏面B2に対向する第2の表面T2と、第2の裏面B2および第2の表面T2をつなぎ、第1の側面S1との間に隙間GPを形成する第2の側面S2とを有する。閉塞部21は隙間GPを閉塞している。

(もっと読む)

炭化珪素基板を有する複合基板の製造方法

【課題】炭化珪素基板を有する複合基板を用いた半導体装置の製造工程において、炭化珪素基板の間の隙間に起因した工程変動を抑制する。

【解決手段】支持部30と第1および第2の炭化珪素基板11、12とを有する接合基板が準備される。第1の炭化珪素基板11は、支持部30に接合された第1の裏面と、第1の裏面に対向する第1の表面と、第1の裏面および第1の表面をつなぐ第1の側面とを有する。第2の炭化珪素基板12は、支持部30に接合された第2の裏面と、第2の裏面に対向する第2の表面と、第2の裏面および第2の表面をつなぎ、第1の側面との間に隙間を形成する第2の側面とを有する。隙間を充填する充填部40が形成される。次に第1および第2の表面が研磨される。次に充填部40が除去される。次に隙間を閉塞する閉塞部が形成される。

(もっと読む)

単結晶炭化珪素基板を有する複合基板

【課題】複合基板を用いた半導体装置の製造において単結晶炭化珪素基板の間の隙間に起因した工程変動を抑制する。

【解決手段】第1の単結晶炭化珪素基板11の第1の辺S1と、第2の単結晶炭化珪素基板12の第2の辺S2とが直線状に並ぶように、第1の単結晶炭化珪素基板11の第1の頂点P1と、第2の単結晶炭化珪素基板12の第2の頂点P2とが互いに突き合わされている。また第1の辺の少なくとも一部と、第2の辺の少なくとも一部とが、第3の単結晶炭化珪素基板13の第3の辺S3に突き合わされている。

(もっと読む)

シリコン薄膜の製造方法、シリコン薄膜太陽電池の製造方法、シリコン薄膜、シリコン薄膜太陽電池

【課題】シリコン薄膜の製造方法、シリコン薄膜太陽電池の製造方法、シリコン薄膜を提供する。

【解決手段】シリコン基板32上にシリコン結晶12の原料ガス28に対して前記シリコン結晶12の成長が不活性な不活性層38を選択的に形成することにより前記シリコン基板32の露出面34と前記不活性層38による不活性面36を形成し、前記原料ガス28のうち前記シリコン基板32における表面分解反応が支配的な性質を有する原料ガス28を前記シリコン基板32に供給して前記シリコン結晶12を前記露出面34から成長させ前記シリコン結晶12が前記シリコン基板を覆う態様でシリコン薄膜10を製造する方法であって、前記露出面34の幅を0.001μmから1μmの範囲で形成することにより、前記シリコン薄膜10を前記シリコン基板32から剥離可能な状態で形成することを特徴とする。

(もっと読む)

トレンチ型金属酸化膜半導体電界効果トランジスタを作製する方法

【課題】トレンチ型金属酸化膜半導体電界効果トランジスタ(MOSFET)が上方向に作製され得る方法を提供すること。

【解決手段】トレンチボトムドーピング(TBD)プロセスおよび/またはトレンチボトム酸化物(TBO)プロセスが、基板および第1のエピタキシャル(エピ)層の形成後に実行され得る。ポリによる封止が、合併型エピタキシャル横方向過成長(MELO)ステップで形成される第2のエピ層の質および純度を改善するために、TBO層の形成後およびMELOステップの前に実行され得る。終点モードを用いたプラズマドライエッチングが、トレンチの深さの均一性を改善するためにTBO層の位置にしたがって実行され得る。

(もっと読む)

半導体ウェハの製造方法、半導体素子の製造方法、半導体ウェハ、半導体素子および電子装置

【課題】 歩留まりが大幅に改善された半導体ウェハの製造方法を提供する。

【解決手段】 本発明の半導体ウェハの製造方法は、基板301上の一部にストライプ状の保護膜302を形成する保護膜形成工程と、前記保護膜形成工程後、前記基板301上における前記保護膜302形成部位以外の部位に半導体結晶を成長させて半導体層を形成する半導体層形成工程とを含み、前記基板301として、前記保護膜302の長さ方向と平行な方向のオフ角θpの絶対値|θp|が、前記保護膜302の長さ方向と直交する方向のオフ角θoの絶対値|θo|よりも小さく、且つ、|θp|≦0.2°を満たすものを用いることを特徴とする。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

非極性または半極性(Ga、Al、In、B)N基板上に成長させられる素子

非極性または半極性の(Ga、Al、In、B)N基板上の(Ga、Al、In、B)N薄膜の成長形態を改良する方法であって、(Ga、Al、In、B)N薄膜は、非極性または半極性の(Ga、Al、In、B)N基板あるいはテンプレート上に直接成長させられ、成長の際に使用されるキャリアガスの一部は、不活性ガスから構成される。非極性または半極性の窒化物LEDおよびダイオードレーザは、本発明によって成長させられる平滑(Ga、Al、In、B)N薄膜上に成長させられてもよい。  (もっと読む)

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ形成工程を有する半導体装置の製造方法において、マスク酸化膜を残したまま、トレンチ内に結晶性の高いエピタキシャル層を埋め込むこと。

【解決手段】n型シリコン基板の表面にn型半導体22を形成し、n型半導体22の表面にマスク酸化膜23およびマスク窒化膜24(マスク積層膜)を形成する。次いで、フォトリソグラフィおよびエッチングによりマスク積層膜を開口し、シリコン基板にトレンチを形成する。次いで、残されたマスク積層膜の幅を狭くして、n型半導体22の、トレンチ25の開口端付近の部分を露出する(第2の露出部)。この状態で、トレンチ内をp型半導体27で埋め込むことで、マスク積層膜の表面にp型半導体27が覆い被さるのを防ぐ。また、n型半導体22の第2の露出部からもp型半導体27が成長するので、p型半導体27の表面にV字状の溝が形成されるのを防ぐ。

(もっと読む)

III−V族窒化物半導体結晶の製造方法およびIII−V族窒化物半導体レーザ素子の製造方法

【課題】基板のAlGaNが露出した最表面上にIII−V族窒化物半導体結晶を成長させるのに適したIII−V族窒化物半導体結晶の製造方法およびその方法を用いたIII−V族窒化物半導体レーザ素子の製造方法を提供する。

【解決手段】水素と窒素とアンモニアとを含み水素の体積比率が水素の体積と窒素の体積との合計体積の0.2以下であるガス雰囲気または窒素とアンモニアとを含み水素を含まないガス雰囲気においてAlGaNが最表面に露出した基板を900℃以上に加熱する加熱工程と、加熱工程後に基板の最表面上にIII−V族窒化物半導体結晶を成長させる結晶成長工程とを含むIII−V族窒化物半導体結晶の製造方法とその方法を用いたIII−V族窒化物半導体レーザ素子の製造方法である。

(もっと読む)

1 - 20 / 40

[ Back to top ]