Fターム[5F152LN01]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706)

Fターム[5F152LN01]の下位に属するFターム

歪みによる悪影響防止 (524)

歪を積極的に利用するもの (168)

その他のもの (2)

Fターム[5F152LN01]に分類される特許

1 - 12 / 12

半導体装置およびその製造方法

【課題】大きなチャネル移動度を有する半導体装置及びその製造方法を提供する。

【解決手段】基板は、ポリタイプ4Hの六方晶の単結晶構造を有する半導体からなる表面SRを有する。基板の表面SRは、面方位(0−33−8)を有する第1の面S1と、第1の面S1につながりかつ第1の面S1の面方位と異なる面方位を有する第2の面S2とが交互に設けられることによって構成されている。ゲート絶縁膜は基板の表面SR上に設けられている。ゲート電極はゲート絶縁膜上に設けられている。

(もっと読む)

複合基板及び複合基板の製造方法

【課題】13族窒化物からなる第1の基板と、セラミックスからなる第2の基板とを貼り合わせた複合基板につき、放熱性をよくすると共に製造時の製造時のプロセスを簡単にする。

【解決手段】セラミックスからなる第2の基板12の表面12aに金属膜23を形成し(c)、この金属膜23を介して13族窒化物からなる第1の基板21と第2の基板12とを接合する(d)。金属膜23は一般に酸化膜と比べて熱伝導率が高いため、こうすることで酸化膜を介して第1の基板21と第2の基板12とを接合した場合と比べて放熱性のよい複合基板10を得ることができる。また、酸化膜を用いないため外方拡散の工程が不要となり、プロセスが簡単になる。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

Znがドープされた3B族窒化物結晶、その製法及び電子デバイス

【課題】高抵抗且つ低転位密度のZnドープ3B族窒化物結晶を提供する。

【解決手段】本発明のZnドープ3B族窒化物結晶は、比抵抗が1×102Ω・cm以上、3B族窒化物結晶中のZn濃度が1.0×1018atoms/cm3以上2×1019atoms/cm3以下、エッチピット密度が5×106/cm2以下のものである。この結晶は、液相法(Naフラックス法)により得ることができる。

(もっと読む)

炭化シリコン膜の製造方法

【課題】良好な膜質であり所望の導電型や導電性に制御された炭化シリコン膜を低コストで効率よく製造する方法を提供する。

【解決手段】本発明の炭化シリコン膜の製造方法は、不純物領域を有する炭化シリコン膜の製造方法である。表層にシリコン膜16aを有する基板11のシリコン膜16aを炭化処理して、炭化された膜を含んだ炭化シリコン膜13を形成する工程を有する。不純物領域になる部分のシリコン膜を炭化処理する前に、この部分に不純物を注入する。

(もっと読む)

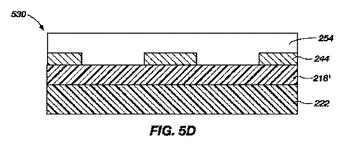

低減した格子ひずみを備えた半導体材料、同様に包含する半導体構造体、デバイス、および、加工された基板を製造する方法

半導体装置を製作する方法または構造体は、従順な材料の層の上に横たわっている半導体材料の構造体を形成することを含み、その後半導体材料構造体を緩和させる従順な材料の粘性を変えて、緩和した半導体材料の連続層を形成する際の種子層として、緩和した半導体材料構造体を利用する。ある実施形態では、半導体材料の層は、III-Vタイプ半導体材料(例えばインジウム窒化ガリウム)から成る。新しい中間構造体が、この種の方法の間、形成される。加工された基板は、緩和した格子の構造体を有する半導体材料の連続層を含む。  (もっと読む)

(もっと読む)

成膜方法

【課題】基板の主表面上に、基板の主表面を構成する材料の格子定数とは格子定数の異なる材料からなる薄膜を成膜することによりヘテロエピタキシャル膜を成膜させる際に、膜の界面付近において組成が急峻に変化していない遷移層が出現する。この遷移層が、ヘテロエピタキシャル膜の界面付近における結晶の特性を劣化させる。

【解決手段】成膜させたい薄膜を構成する材料の格子定数と、薄膜が成膜される基板の一方の主表面を構成する材料の格子定数とに応じて、主表面に沿った方向に対して基板を湾曲させる。そして、基板を湾曲させた状態で、その基板の一方の主表面上に薄膜を成膜させる。

(もっと読む)

半導体電子デバイス

【課題】耐圧性が高く反りが小さい半導体電子デバイスを提供すること。

【解決手段】基板と、前記基板上に形成された、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記基板と前記バッファ層との間に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、を備え、前記バッファ層において、前記第一半導体層の層厚が不均一であるとともに、該第一半導体層のうち少なくとも一つが、前記基板に対して発生させる反りの方向が反転する臨界厚さよりも厚い層厚を有する。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

基板上に歪層を製造する方法と層構造

【課題】

ウエーハ接着及び/又はウエーハ研磨なしに基板上に高い品質の歪層を製造する簡単な方法を提供すること。

【解決手段】

この発明は、歪をもたせる層に隣接した層に欠陥領域を形成する工程と、歪をもたせる層に少なくとも隣接した層を緩和させる工程とにより、基板上に歪層を製造する方法に関する。その歪層は別のエピタキシャル層に配置されることができる。そのように形成された層構造は種々の構成要素に好ましく適している。  (もっと読む)

(もっと読む)

整合した熱膨張係数を有する複合基体上の付着されたウエハ構造を有する装置構造を処理する方法

ウエハ構造が互いに結合されている2以上の基体層を含む複合基体構造上に付着されている。第1の基体層はウエハの横断方向熱膨張係数よりも大きい第1の基体層材料横断方向熱膨張係数を有する第1の基体層材料で形成され、第2の基体層はウエハの横断方向熱膨張係数よりも小さい横断方向に平行に測定された第2の基体層材料横断方向熱膨張係数を有する第2の基体層材料で形成されている。基体層は、基体の横断方向熱膨張係数のウエハの横断方向熱膨張係数との差が約2×10-6/°F以下となるような相対的比率で構成されている。  (もっと読む)

(もっと読む)

格子整合されなかった基板上に応力緩和層構造を形成する方法及び電子素子及び/又は光導電素子内でのこのような層組織の使用

【課題】

本発明は、その都度異なる格子構造を有する基板上に1つ又は多数の層を有する単結晶応力緩和層構造を形成する方法に関する。特殊な構造では、この方法は、好ましくは応力緩和したSi−Ge層構造上にひずみシリコンを形成するために使用される。さらに本発明は、このような層組織を、例えばMOSFET,MODFET,共振トンネルダイオード,フォト検出器や量子カスケード・レーザのような素子で使用することに関する。  (もっと読む)

(もっと読む)

1 - 12 / 12

[ Back to top ]