Fターム[5F152LN07]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪を積極的に利用するもの (168)

Fターム[5F152LN07]の下位に属するFターム

Fターム[5F152LN07]に分類される特許

1 - 20 / 39

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

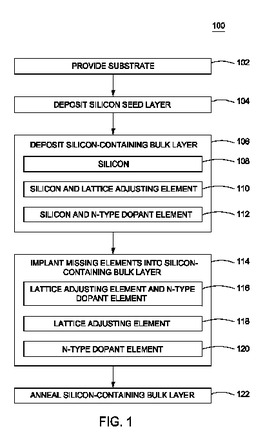

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化したMOSFETにおいて、ボイドやシームの発生無しに素子分離領域

に絶縁膜を埋め込むことができ、キャリアの移動度向上が可能な半導体装置及び半導体装

置の製造方法を提供する。

【解決手段】 本発明では、シリコンを主成分とする半導体基板101と、半導体基板の

素子形成領域上にゲート絶縁膜105を介して形成されたゲート電極平行方向に伸びるゲ

ート電極106と、素子形成領域に前記ゲート電極下のチャネル領域を挟むように前記半

導体基板中に形成された拡散層と、素子形成領域を囲むように設けられ、ゲート電極平行

方向に対して垂直なゲート電極垂直方向に伸びる第1の素子分離絶縁膜112と、ゲート

電極平行方向に伸び、第1の素子分離絶縁膜と幅または深さが異なる第2の素子分離絶縁

膜113とからなる素子分離絶縁膜とを有する半導体装置が得られる。

(もっと読む)

高ゲルマニウム濃度のSiGeストレッサの形成方法

【課題】SiGeストレッサの形成方法と集積回路のトランジスタ構造を提供する。

【解決手段】SiGeストレッサを形成する方法であって、前記方法は、ソース領域とドレイン領域間にチャネルを有する半導体基板上のソース領域とドレイン領域の少なくとも1つに第1SiGe層を堆積するステップ、及び前記第1SiGe層の上部を酸化層に変換し、前記第1SiGe層の底部を第2SiGe層に変換するステップを含み、前記第2SiGe層は、前記第1SiGe層より高いGe濃度を有する方法。

(もっと読む)

減少した転位パイルアップを有する半導体ヘテロ構造および関連した方法

【課題】緩和した格子不整合の半導体へテロ構造を提供すること。

【解決手段】組成的に勾配した半導体層における転位パイルアップは、減少もしくは実質的に除かれ、これによって、増加した半導体デバイス歩合および製造性に導く。このことは、組成的に勾配したバッファ層の後に続く成長および緩和の前のスタート層としておよび/または組成的に勾配した層の成長および緩和中の少なくとも1つの中間層としてその表面にわたり実質的に均一に分布する複数のスレッディング転位を有する半導体層を導入することによって達成される。この半導体層は、半導体層の表面に近接して位置するシード層、およびそこに均一的に分布するレッディング転位を有することを含み得る。

(もっと読む)

Ge膜付きSOI基板の製造方法及びGe膜付きSOI基板

【課題】引っ張り応力を高めたGe膜を有する基板を提供する。

【解決手段】絶縁性基板である石英基板又はガラス基板上に、シリコン薄膜を備えるSOI基板を用意する工程と、ゲルマニウムを上記SOI基板のシリコン薄膜の上にエピタキシャル成長させてゲルマニウム膜を形成する工程とを少なくとも含んでなるGe膜付きSOI基板の製造方法を提供する。また、絶縁性基板である石英基板又はガラス基板上のシリコン薄膜を備えるSOI基板と、上記SOQ基板のシリコン薄膜の上にエピタキシャル成長させたゲルマニウム膜を備える半導体用Ge膜付きSOI基板を提供する。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】格子緩和又は一部格子緩和した歪緩和SiGe層の形成を可能にし、これによって転位欠陥を少なくするようにした半導体基板の製造方法及び半導体基板を提供する。

【解決手段】Si基板10上に絶縁層11を介してSiGe層を備えた半導体基板の製造方法である。Si基板上に前記絶縁層11を介してSi層12を備えたSOI基板13のSi層12上に、第1のSiGe層14を形成するSiGe成膜工程と、SiGe成膜工程後、熱処理を施し、第1のSiGe層14中のGeをSi層12中に拡散・濃縮させ、SiGe層となる第2のSiGe層16を形成する拡散工程と、を有する。第1のSiGe層形成工程では、第1のSiGe層14中のGe濃度を5%以下にする。

(もっと読む)

半導体装置の製造方法

【課題】半導体製造工程におけるストレス印加およびアニールによる転位、結晶欠陥を抑え、チャネル領域において良好なストレスを印加するとともに、低抵抗化と浅接合化の両立を図ることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法において、半導体基板表面に前記半導体基板表面の面積に対する開口率が5〜30%の開口部を形成する工程と、前記開口部内に15〜25%の範囲の濃度で前記半導体基板を構成する原子と異なる格子定数を有する第2の原子を含む混晶からなるエピタキシャル層を形成する工程と、前記エピタキシャル層にイオン注入する工程と、所定の温度Tで活性化アニールを行う工程とを備え、前記所定の温度Tは、1150℃以上かつT≦1E−5exp(21541/T)からなる関係を満たす。

(もっと読む)

エピタキシャル成長のための基板の作成方法

【課題】本発明は、補助基板上に緩和エピタキシャルベース層を得ることを含む、エピタキシャル成長のための基板の作製方法に関する。本発明の目的は、望ましい格子パラメータを有する材料が、異なる格子パラメータを有する別の材料の上で、より効率的に、熱力学的及び結晶学的に高い安定性を有してエピタキシャル成長することを可能にする基板を作ることにある。

【解決手段】この目的は、上記のタイプの方法であって、エピタキシャルベース層の少なくとも一部をキャリア基板上に移してベース基板を形成することと;エピタキシャルベース層の材料をキャリア基板上でさらに成長させることとをさらに含む方法により達成される。

(もっと読む)

歪みシリコン層が形成されたシリコンウェーハ及びその製造方法

【課題】シリコン以外の元素の層を堆積して形成していなくても十分な歪み量の歪みシリコン層を有するシリコンウェーハ及びその製造方法を低コストで提供することを目的とする。

【解決手段】歪みシリコン層を有するシリコンウェーハの製造方法であって、少なくとも、シリコンウェーハにイオンを注入することによって該シリコンウェーハの表面層をイオン注入層とし面内方向の格子を歪ませた後、前記シリコンウェーハのイオン注入された面上にシリコンを気相成長させることにより歪みシリコン層を成長させることを特徴とする歪みシリコン層を有するシリコンウェーハの製造方法を提供する。

(もっと読む)

結晶成長シミュレーター

【課題】次世代の光半導体デバイス開発の基礎になるものと期待されている、量子ドットの形成過程について、従来の静的な計算結果ではなく、動的過程を解明するための有効な計算方法を提供する。

【解決手段】対象を三領域に分割し、そのそれぞれで別系統の計算手法を適用することにより、マルチスケールかつハイブリッドな計算機シミュレーションの方法を実現している。それらのうち、最上部の表面層領域における原子拡散により引き起こされた歪みの効果を、中間部のサブメッシュ上の分離力学計算領域に伝え、この領域で緩和をおこなった結果を、下部領域にある有限要素法の計算部分に伝達することにより、隔たった領域間の歪みの相互作用の効果を、中間部を通じて表面領域にフィードバックさせるようなアルゴリズムが構成できる。また、そのアルゴリズムを実現するシステムを構築する。

(もっと読む)

貼り合わせ基板の製造方法

【課題】従来より大きな引っ張り歪みが導入されたSi1−xGex(0<x≦1)薄膜を有する貼り合わせ基板の製造方法を提供する。

【解決手段】少なくとも、ドナーウェーハと、ドナーウェーハより熱膨張率の低いハンドルウェーハとを準備する工程と、ドナーウェーハに水素イオン又は希ガスイオンあるいはこれらの両方を注入してイオン注入層を形成する工程と、ドナーウェーハとハンドルウェーハの少なくとも一方の貼り合わせ面にプラズマ活性化処理を行う工程と、ドナーウェーハとハンドルウェーハとを貼り合わせる工程と、ドナーウェーハのイオン注入層に機械的衝撃を加えて剥離を行う工程と、ドナーウェーハの剥離面に表面処理を行う工程と、剥離面上に、Si1−xGex(0<x≦1)薄膜をエピタキシャル成長させることによって、貼り合わせウェーハ上に歪みSi1−xGex(0<x≦1)薄膜を形成する工程とを有する貼り合わせ基板の製造方法。

(もっと読む)

シリコン含有膜を選択的に堆積する方法

1つの実施形態は、単結晶膜を選択的に堆積するための方法を提供する。この方法は、第1の表面形態を有する第1の表面およびこの第1の表面形態とは異なる第2の表面形態を有する第2の表面を含む基体を準備する工程を含む。シリコン前駆体[108]およびBCl3[134]は相互混合され、これにより供給ガスが形成される。この供給ガスは、化学気相成長条件[122]下でこの基体へ導入される。Si含有層は、供給ガス[120]を導入することにより、第2の表面上に堆積することなく、第1の表面上に選択的に堆積される。 (もっと読む)

半導体ヘテロ構造

【課題】より小さな表面凹凸をもつ半導体ヘテロ構造を提供すること。

【解決手段】本発明は、第1の面内格子定数をもつ支持基板と、該支持基板上に形成されていて、上部に格子緩和状態おいて第2の面内格子定数をもつ緩衝構造と、および該緩衝構造上に形成された組成非傾斜層の多層積層とを備えた半導体ヘテロ構造に関するものである。表面凹凸の少ない、前記のタイプの半導体ヘテロ構造を提供することが本発明の目的である。前記の目的は、該組成非傾斜層が歪み層であり、かつ、該歪み層が前記第1および第2の格子定数の中間の第3の面内格子定数を格子緩和状態において有する半導体材料の、歪を有する平坦化層を少なくとも1つ含んで構成されることを特徴とする、前記のタイプのヘテロ構造によって達成される。

(もっと読む)

シリコンを含有するエピタキシャル層の形成

【課題】 シリコンを含有するエピタキシャル層の形成方法を提供する。

【解決手段】 特定の実施形態は、半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおけるエピタキシャル層の形成と処理に関する。特定の実施形態において、エピタキシャル層の形成は、プロセスチャンバ内の基板をシランや高次シランのような二つ以上のシリコン源を含む堆積ガスにさらすことを含んでいる。実施形態は、エピタキシャル層の形成中にリンドーパントのようなドーパント源を流すステップと、リンドーパントを含まずにシリコン源ガスによる堆積を続けるステップとを含む。

(もっと読む)

ヘテロ構造内で空孔拡散を制限する方法

【課題】半導体材料からなる少なくとも第1の層(102)を、第1の層の材料とは異なる材料からなる第2の層(101)上に備えるヘテロ構造を製作する方法に関し、半導体材料の元素が、空孔機構によって、第1の層(102)内でまた隣接する層内に拡散するのを防止すること。

【解決手段】本発明の方法は、前記第1の層の元素が空孔拡散するのを制限するために、第1の層(102)を格子間欠陥(105a)で富化させるためのステップ(S2)を含む。

(もっと読む)

半導体材料で作られた基板の表面上または基板内の歪みを調節するプロセス

【課題】基板上の歪み層の歪みを調節するプロセスを提供する。

【解決手段】このプロセスは、歪みが調節される歪み層の1つ以上の領域を特定するステップと、このように特定された歪み層の領域の少なくとも1つに元素を注入するステップと、1つ以上の注入領域に注入によって生じた結晶欠陥を矯正するのに十分な長さの時間、維持された温度で基板および歪み層をアニールするステップとを含む事により歪みを局所的に調節する。

(もっと読む)

基板、方法(1つまたは複数のSOI領域またはバルク半導体領域あるいはその両方を有するハイブリッド結晶表面配向基板)

【課題】単一スタック内で互いに結合された複数の絶縁体上半導体(SOI)ウエハを含む半導体デバイス用の基板を提供すること。

【解決手段】このスタックの遠位端は、第1表面配向を有するある厚さの第1半導体層を伴う第1のSOI領域を含む。この単一スタックの表面はさらに、非SOI領域、または少なくとも1つの第2のSOI領域、あるいはその両方を含み得る。この非SOI領域は、単一スタックのすべての絶縁体層を貫通して延び、かつ、第1シリコン層と異なる厚さを有するバルク・シリコンを含み得る。第2のSOI領域はそれぞれ、厚さが第1半導体層の厚さと異なるか、または表面配向が第1表面配向と異なるか、あるいはその両方とも異なる第2の半導体層を有する。そのため、この基板により、表面配向が異なるか、または厚さが異なるか、あるいはバルクまたはSOIと構造が異なるか、あるいはこれら異なるものが組み合わされた最適な基板領域上に異なるデバイスを形成することができる。

(もっと読む)

1 - 20 / 39

[ Back to top ]