Fターム[5F152LN04]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪みによる悪影響防止 (524) | 凹凸の低減 (54)

Fターム[5F152LN04]に分類される特許

1 - 20 / 54

赤色発光半導体素子とその製造方法

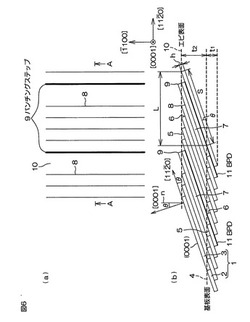

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

半導体装置

【課題】シリコン基板直上の窒化アルミニウム層の平坦性が低いことに起因する信頼性の低下が抑制された半導体装置を提供する。

【解決手段】シリコン基板10と、シリコン基板上に配置された、不純物としてシリコンがドープされた領域を有する窒化アルミニウム層20と、窒化アルミニウム層上に配置された、複数の窒化物半導体膜が積層された構造のバッファ層30と、バッファ層上に配置された、窒化物半導体からなる半導体機能層40とを備える。

(もっと読む)

ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法

【課題】バウの制御のためだけでなく、SiGeエピタキシャル層の品質を改善するために、特にSi基板上に堆積されたSiGe層のクロスハッチ及び表面ラフネスを低減するために、背面層によって形成された応力を用いる適切な解決策を提供する。

【解決手段】第1の面及び第2の面を有する基板10、前記基板の第1の面に堆積された完全に又は部分的に緩和されたヘテロエピタキシャル層20、及び前記基板の第2の面に堆積された応力相殺層30を有する、半導体ウェハ。

(もっと読む)

半導体ウエーハ及び半導体素子及びその製造方法

【課題】クラックが少なく表面の平坦性が良好な半導体ウエーハ及び半導体装置及びその製造方法を提供する。

【解決手段】半導体ウエーハは、基板2と、基板2の一方の主面上に配置され且つ化合物半導体で形成されたバッファ領域3と、バッファ領域3の上に配置され且つ化合物半導体で形成された主半導体領域4とを有する半導体ウエーハであって、バッファ領域3は、第1の多層構造バッファ領域5と、基板と第1の多層構造バッファ領域5との間に配置された第2の多層構造バッファ領域8とから成る。

(もっと読む)

エピタキシャル成長用基板およびエピタキシャル成長用基板の製造方法

【課題】平坦性、結晶性および配向性に優れ、厚さ方向の熱伝導率が高く放熱性に優れたエピタキシャル成長用基板およびその製造方法を提供する。

【解決手段】炭素基板の少なくとも一方の主表面に、算術平均表面粗さRaが0.05μm以下で、表面粗さの最大値Ryが0.5μm以下であり、X線回折法による(0002)面のロッキングカーブの半値幅が1.5度以下であり、ラマンスペクトルにおけるGバンドのピーク強度に対するDバンドのピーク強度の比が0.01以下である高結晶グラファイト層を形成してなることを特徴とするエピタキシャル成長用基板である。

(もっと読む)

窒化ガリウム系半導体基板の製造方法

【課題】貫通ピットの無い窒化ガリウム系半導体基板を安価に得ることができる窒化ガリウム系半導体基板の製造方法を提供する。

【解決手段】窒化ガリウム系半導体基板の製造方法であって、気相成長装置内に、表面にピット25を生じた窒化ガリウム系半導体層20を有する基板を準備する第1の工程と、前記気相成長装置内で、前記窒化ガリウム系半導体層20上に、非晶質又は多結晶のIII族窒化物のピット埋込層30を形成して前記ピット25を埋める第2の工程と、前記ピット埋込層30を研磨により除去して前記窒化ガリウム系半導体層20の表面を露出させる第3の工程と、を具備する。

(もっと読む)

デバイスのためのガリウム及び窒素含有超薄型エピタキシャル構造のための高速成長方法及び構造

ガリウム及び窒素含有材料の高速成長のための方法が記載される。本方法は、バルクガリウム及び窒素含有基板を提供することを含んでいる。第1の厚さの第1のエピタキシャル材料が、好ましくは擬似形態的プロセスによって、基板上に形成される。本方法は、第1の層上に第2のエピタキシャル層をも形成し、これによってスタック構造がもたらされる。スタック構造は、約2ミクロン未満の全体厚さで構成される。 (もっと読む)

異種基板、それを利用した窒化物系半導体素子及びその製造方法

本発明は、異種基板と、それを利用した窒化物系半導体素子及びその製造方法に関し、異種基板の無極性または半極性面に結晶成長モードを調節し、高品質の無極性または半極性窒化物層を形成するためのものである。無極性または半極性面のうち1つを有するベース基板を準備し、用意したベース基板の面に窒化物系結晶成長核層を形成する。結晶成長核層の上に第1バッファー層を成長させ、且つ、水平方向に比べて垂直方向にさらに速く成長させる。第1バッファー層上に水平成長層を成長させ、且つ、垂直方向に比べて水平方向にさらに速く成長させる。また、水平成長層上に第2バッファー層を成長させる。この際、第1バッファー層上の水平成長層と第2バッファー層との間に複数の孔を有する窒化シリコン層をさらに形成することができる。  (もっと読む)

(もっと読む)

非極性または半極性(Ga、Al、In、B)N基板上に成長させられる素子

非極性または半極性の(Ga、Al、In、B)N基板上の(Ga、Al、In、B)N薄膜の成長形態を改良する方法であって、(Ga、Al、In、B)N薄膜は、非極性または半極性の(Ga、Al、In、B)N基板あるいはテンプレート上に直接成長させられ、成長の際に使用されるキャリアガスの一部は、不活性ガスから構成される。非極性または半極性の窒化物LEDおよびダイオードレーザは、本発明によって成長させられる平滑(Ga、Al、In、B)N薄膜上に成長させられてもよい。  (もっと読む)

(もっと読む)

グラフェン層が成長された基板およびそれを用いた電子・光集積回路装置

【課題】グラフェン層成膜の大面積化や基板材質の選択自由度の拡大、製造の低コスト化を実現するグラフェン層が成長された基板およびそれを用いた電子・光集積回路装置を提供する。

【解決手段】本発明に係るグラフェン層が成長された基板は、単層または複数層からなるグラフェン層が成長された基板であって、前記グラフェン層は前記基板の表面に対して略平行に成長しており、前記グラフェン層に対向する前記基板の最表面には金属酸化物の原子層が存在し、前記グラフェン層の前記基板に隣接する層と前記金属酸化物の原子層との層間距離が0.34 nm以下であることを特徴とする。また、前記金属酸化物の原子層の算術平均表面粗さRaが1 nm以下であることが好ましい。

(もっと読む)

III族窒化物半導体の製造方法,III族窒化物半導体素子の製造方法,III族窒化物半導体とIII族窒化物半導体素子

【課題】 III族窒化物半導体の結晶層を含む半導体素子において品質低下を防止可能であり、かつ製造効率に優れたIII族窒化物半導体の製造方法、III族窒化物半導体素子の製造方法、III族窒化物半導体およびIII族窒化物半導体素子を提供する。

【解決手段】

下地層の上面にIII族窒化物の非結晶層を形成する非結晶層形成工程(A)と、

前記非結晶層の上面に保護層を形成する保護層形成工程(B)と、

前記非結晶層の一部をエッチングにより除去するエッチング工程(C)と、

前記保護層が形成された状態で前記非結晶層を熱処理して結晶化することによりIII族窒化物半導体の結晶層に変換する半導体結晶層形成工程(D)と、を含むことを特徴とするIII族窒化物半導体の製造方法。

(もっと読む)

歪Si−SOI基板の製造方法及び該方法により製造された歪Si−SOI基板

【課題】歪Si層表面が平坦で欠陥が少ない歪Si−SOI基板を簡便に製造する。

【解決手段】SOI基板10の第1Si層13上にSiGe混晶層14を形成し、SiGe混晶層上に第1Si層の厚さより厚い55〜550nmの厚さの第2Si層16を形成する。基板を酸化性雰囲気下又は不活性ガス雰囲気下、950℃以上で熱処理してSiGe混晶層を溶融するとともに第1Si層と第2Si層の一部にGeを拡散する。基板を降温して溶融したSiGe混晶層18,19,21を固化し、固化したSiGe混晶層22の上に歪Si層16aが形成された歪Si−SOI基板23を得る。

(もっと読む)

ウェーハおよびウェーハの製造方法

【課題】異なる格子の基板上に成長した良質なエピタキシャル層を備えたウェーハおよびウェーハ製造方法の提供。

【解決手段】単結晶の第1の材料の基板はオンアクシスシリコン基板であり、オンアクシスシリコン基板上に第2の材料を成長させるウェーハの製造方法に関し、第2の材料が、第1の材料上にエピタキシャル成長し、第1の材料の格子とは異なる格子を持っている。オンアクシスシリコン基板を研磨ステップ104で研磨して、ウェーハ表面粗さを増大させる。SiGe層である傾斜バッファ層及び緩和層をウェーハ上に形成した後、CMP最終研磨108を実施する。上述のタイプの方法により解決され、基板の最終表面仕上げの前に第2の材料の成長を実施する。

(もっと読む)

窒素化合物半導体基板の製造方法および窒素化合物半導体基板

【課題】結晶性のよい窒素化合物半導体層が得られ、しかも低コストで生産性のよい窒素化合物半導体基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層3と埋め込み絶縁層4とを有するSi基板1を準備する工程と、上記Si基板1を炭素系ガス雰囲気中で加熱して上記表面Si層3を単結晶SiC層6に変成させる際に、上記埋め込み絶縁層4との界面8近傍のSi層を残存Si層5として残す工程と、表面の単結晶SiCに対してさらに窒素化合物半導体層15をエピタキシャル成長させる工程とを行なう。

(もっと読む)

III−V族窒化物半導体結晶の製造方法およびIII−V族窒化物半導体レーザ素子の製造方法

【課題】基板のAlGaNが露出した最表面上にIII−V族窒化物半導体結晶を成長させるのに適したIII−V族窒化物半導体結晶の製造方法およびその方法を用いたIII−V族窒化物半導体レーザ素子の製造方法を提供する。

【解決手段】水素と窒素とアンモニアとを含み水素の体積比率が水素の体積と窒素の体積との合計体積の0.2以下であるガス雰囲気または窒素とアンモニアとを含み水素を含まないガス雰囲気においてAlGaNが最表面に露出した基板を900℃以上に加熱する加熱工程と、加熱工程後に基板の最表面上にIII−V族窒化物半導体結晶を成長させる結晶成長工程とを含むIII−V族窒化物半導体結晶の製造方法とその方法を用いたIII−V族窒化物半導体レーザ素子の製造方法である。

(もっと読む)

ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法

【課題】バウの制御のためだけでなく、SiGeエピタキシャル層の品質を改善するために、特にSi基板上に堆積されたSiGe層のクロスハッチ及び表面ラフネスを低減するために、背面層によって形成された応力を用いる適切な解決策を提供すること。

【解決手段】第1の面及び第2の面を有する基板10、前記基板の第1の面に堆積された完全に又は部分的に緩和されたヘテロエピタキシャル層20、及び前記基板の第2の面に堆積された応力相殺層30を有する、半導体ウェハ。

(もっと読む)

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系単結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、酸化物からなる部材を備えたSiを主成分とする半導体基板の表面をSiおよびGeのうちの少なくともいずれか1つを含むハロゲン含有ガスに曝す工程と、前記半導体基板の前記表面をハロゲン含有ガスに曝し始めた後、前記表面をハロゲンを含まないSi含有ガスおよびハロゲンを含まないGe含有ガスのうち少なくともいずれか1つを含む雰囲気に曝し、前記表面にSiおよびGeのうち少なくともいずれか1つを含む結晶膜をエピタキシャル成長させる工程と、を含む。

(もっと読む)

III−V族化合物半導体層の製造方法、半導体光素子の製造方法、および半導体光素子

【課題】N原子を含むIII−V族化合物半導体層の結晶性をより向上させ得るIII−V族化合物半導体層の製造方法、半導体光素子の製造方法、および半導体光素子を提供する。

【解決手段】N原子を含むIII−V族化合物半導体層を製造する方法であって、III−V族化合物半導体層を構成する半導体結晶を半導体基板上に成長させてエピタキシャルウェハ1を形成する工程と、エピタキシャルウェハ1上におもり104を載せることで該半導体結晶に対して荷重を付与しつつ、該半導体結晶に対しその成長温度より高い温度で熱処理を行うアニール工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

1 - 20 / 54

[ Back to top ]