Fターム[5F152LN11]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | バッファ層、動作層 (308)

Fターム[5F152LN11]の下位に属するFターム

Fターム[5F152LN11]に分類される特許

21 - 35 / 35

窒化物半導体成長用基板

高品質の窒化物半導体結晶層を得ることができる窒化物半導体成長用基板を提供する。本発明の一実施形態に係る、サファイア基板(1)上に窒化物半導体層を成長させるための窒化物半導体成長用基板は、サファイア基板(1)上に別途に設けたAl2O3層(2)と、第1の層であるAlON層(3)と、第2の層であるAlN層(4)とを備える。第1の層および第2の層については、AlON層(3)とAlN層(4)との順序でAl2O3層(2)上に積層させる。  (もっと読む)

(もっと読む)

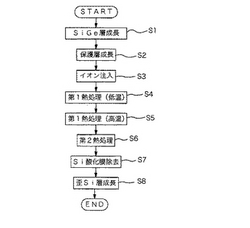

歪Si−SOI基板の製造方法および該方法により製造された歪Si−SOI基板

【課題】 表面が平坦で欠陥が少ない歪Si−SOI基板およびその製造方法を提供する。

【解決手段】 Si層13と埋め込み酸化膜12とを有するSOI基板10に、SiGe混晶層14を成長する工程と、SiGe混晶層14の表面に保護膜15,16を形成する工程と、Si層13と埋め込み酸化膜12界面近傍に軽元素をイオン注入する工程と、400〜1000℃での熱処理を行う第1熱処理工程と、1050℃以上で酸化雰囲気の熱処理を行う第2熱処理工程と、1050℃以上で不活性雰囲気の熱処理をおこなう第3熱処理工程と、表面のSi酸化膜18を除去する工程と、歪Si層19を形成する工程と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SOI基板を用いることなく、絶縁体上に形成される半導体層の面積を拡大する。

【解決手段】 開口部7を介して空洞部9内の半導体基板1および第2半導体層3の熱酸化を行うことにより、半導体基板1と第2半導体層3との間の空洞部9に埋め込み絶縁膜10を形成した後、ソース/ドレイン層25a、25bの表面に露出している埋め込み絶縁膜10、13および第2半導体層3をパターニングすることにより、開口部7の周囲のソース/ドレイン層25a、25bの側壁を露出させるコンタクトホール26を形成し、コンタクトホール26を介してソース/ドレイン層25a、25bにそれぞれ接続された配線層27a、27bを形成する。

(もっと読む)

薄層を除去した後の多層構造を備えるウェハのリサイクル

半導体材料から選ばれた材料を含む有用層を除去した後にドナーウェハ(10)をリサイクル方法であって、ドナーウェハ(10)は基板(1)と多層構造(I)とを順次に備え、除去前の多層構造(I)は除去すべき有用層を備え、そのプロセスは除去が行われた側での物質除去を含み、物質除去の後に多層構造(I’)の少なくとも部分が残り、このバッファ構造(I’)の少なくとも部分は除去することができる別の有用層を1つ以上含み、有用層を再形成する補足的段階をともなわないことを特徴とする。本書はまた:本発明による少なくとも1つのリサイクル可能ドナーウェハ(10)から薄層を除去する方法、本発明によるリサイクル可能ドナーウェハ(10)に関する。  (もっと読む)

(もっと読む)

窒化物系半導体素子及びその製造方法

窒化物系半導体素子を形成するためにp型不純物がドープされ且つ十分な導電性を有するp型シリコン基板(1)を用意する。シリコン基板(1)の上に、AlNから成る第1のバッファ層(11)、n−InGaNから成る第2のバッファ層(12)、n−GaNから成るn型窒化物半導体層(13)、活性層(14)、及びp−GaNから成るp型窒化物半導体層(15)を順次にエピタキシャル成長させる。エピタキシャル成長時の加熱処理によって第1の層(11)のAl、第2の層12のGa及びInがp型シリコン基板(1)に拡散してp型シリコン基板(1)とバッファ層(11)との間に合金層(2)が形成される。Al,Ga,Inは合金層(2)に隣接するp型シリコン基板(1)の内部にも拡散するが、Al,Ga,Inはシリコンに対してp型不純物として機能し且つシリコン基板(1)がp型であるので、シリコン基板(1)中にpn接合が形成されない。この結果、窒化物系半導体素子の駆動電圧が低くなる。  (もっと読む)

(もっと読む)

半導体基板及びその製造方法

【課題】一方でドナーウェハ上の極めて厚いシリコン−ゲルマニウム層のコストのかかる析出を必要とせず、他方でハンドルウェハ上に薄い層を移設した後にわずかな表面粗さが生じる、sSOI基板又はSGOI基板を製造するための有効な方法を提供する。

【解決手段】単結晶シリコンウェハと、その表面上に存在する、シリコン及びゲルマニウムを含有する緩和された単結晶層(この場合、前記層の表面のゲルマニウム含有量は10質量%〜100質量%の範囲内にある)と、及び前記表面の下に周期的に配置された中空室の層とを有する半導体基板

(もっと読む)

半導体エピタキシャル基板

【目的】エピタキシャル成長面の凹凸が小さく、良好な特性を有し、生産性に優れた半導体エピタキシャル基板を提供する。

【構成】基板の結晶学的面方位が、1つの{100}面の結晶学的面方位から傾いており、その傾きの大きさが0.05°以上0.6°以下である単結晶砒化ガリウム基板上にエピタキシャル成長により結晶が形成されており、エピタキシャル結晶の少なくとも一部がInx Ga(1-x) As結晶(ただし0<x<1)であり、かつエピタキシャル成長が熱分解気相成長方法によって行われることを特徴とする半導体エピタキシャル基板。

(もっと読む)

Si1−x−yGexCy層において炭素を安定させる方法

【課題】 炭素ドープシリコンベースの膜の熱的安定性を引っ張り応力と圧縮応力との両方を用いて様々な半導体用途において使用するために改善すること。

【解決手段】 層はSi1−x−yGexCyを含み、層内の炭素は安定した状態にあり、半導体デバイス内の層を提供する方法は、シリコン基板(12)を準備することと、SiGeC前駆物質を準備することと、前駆物質からシリコン基板上にSi1−x−yGexCy層(14)を形成することと、Si1−x−yGexCy層上に最上位シリコン層(16)を形成することと、半導体デバイスを完成することとを包含する。

(もっと読む)

窒化物半導体ウエハ又は窒化物半導体素子の製造方法、それにより得られる窒化物半導体ウエハ又は窒化物半導体素子、並びにそれに用いるレーザ照射装置

【課題】異種基板を剥離する工程を含む窒化物半導体ウエハ又は窒化物半導体素子の製造方法において、異種基板剥離時の窒化物半導体層の破断を抑制する方法を提供する。

【解決手段】窒化物半導体と異なる異種基板16上に成長された窒化物半導体層18から、前記異種基板16−窒化物半導体層18界面に酸又はアルカリであるエッチング溶液を供給しながら、異種基板16側から前記窒化物半導体層18のバンドギャップ波長よりも短波長のレーザ光を照射することによって異種基板16の剥離を行う。

(もっと読む)

単層および多層の単結晶シリコンおよびシリコンデバイスをプラスチック上に犠牲ガラスを用いて製造する方法

【課題】 シリコンおよびシリコンデバイスをプラスチック基板上に好適に製造する方法を提供する。

【解決手段】 シリコン−オン−プラスチック層を層移転から製造する方法は、シリコン基板(12)上にSiXGe(1−X)(0≦x≦1)層(14)を堆積すること、シリコン層(22)を堆積すること、シリコン基板に水素イオンを注入すること、ガラス基板(34)をシリコン層(22)に結合すること、ウェハを分割すること、シリコン層(22)とSiGe層(14)の一部分とを除去すること、シリコン−オン−グラス・ウェハのシリコン側に誘電体を堆積すること、接着剤を供給し、該ウェハのシリコン側にプラスチック基板を結合すること、結合した該ウェハのガラス側からガラス(34)を除去し、シリコン−オン−プラスチック・ウェハを形成することを包含する。本発明の方法の最後の数ステップを繰り返すことによって多層構造が製造され得る。

(もっと読む)

緩和SiGe層の形成方法

【課題】 緩和SiGe合金層において、積層欠陥およびマイクロツイン等の平面欠陥の形成を抑えるための方法を提供すること。

【解決手段】 平面欠陥密度を低下させた、実質的に緩和したSiGe合金層を製造する方法を開示する。本発明の方法は、Si含有基板の表面上に歪みGe含有層を形成するステップと、Ge含有層/Si含有基板の界面にまたは界面の下にイオンを注入するステップと、加熱を行って、平面欠陥密度が低下した、実質的に緩和したSiGe合金層を形成するステップと、を含む。また、平面欠陥密度が低下したSiGe層を有する実質的に緩和したSiGe−オン−インシュレータおよびこれを含むヘテロ構造も提供する。

(もっと読む)

CMOSにおいてキャリア移動度を向上させる方法(MOSFETデバイスの圧縮SiGe<110>成長および構造)

【課題】 CMOSにおいてホールおよび電子の移動度を向上させる方法を提供する。

【解決手段】 キャリアを伝導させるための構造およびこれを形成するための方法を記載する。これは、 <110>において上面を有するSiまたはSiGeの単結晶基板と、この基板とはGe濃度が異なるSiGeの擬似格子整合またはエピタキシャル層と、を含み、これによって擬似格子整合層に歪みがかかっている。半導体エピタキシャル層を形成するための方法を記述する。これは、急速熱化学的気相堆積(RTCVD)ツールにおいて擬似格子整合またはエピタキシャル層を形成するステップを含み、ツール内の温度を約600℃まで上昇させ、Si含有ガスおよびGe含有ガスの双方を導入する。エピタキシャル堆積のために基板を化学的に準備するための方法を記述する。これは、基板を、オゾン、希薄HF、脱イオン化水、HCl酸および脱イオン化水を含む一連の槽にそれぞれ浸漬し、その後、基板を不活性雰囲気において乾燥させて、不純物のない、RMS粗さが約0.1nm未満の基板表面を得る。

(もっと読む)

GaN系窒化膜を形成する方法

本発明は、サファイヤ基板上にSiaCbNc

(c,b>0,a≧0)の組成からなる第1層を形成する第1段階と、SiaCbNc

(c,b>0,a≧0)の組成からなる第1層の上にGaN成分を含む窒化膜を形成する第2段階と、を含むことを特徴とするGaN系窒化膜の形成方法に関する。  (もっと読む)

(もっと読む)

選択されたパラメータを有するSiGeオン・インシュレータ(SGOI)基板を製作する方法(酸化、薄型化、およびエピタキシャル再成長の組み合わせを使用するSiGe格子工学)

【課題】 SiGe厚さとGe比とひずみ緩和との相互依存を切り離すために格子工学が使用される、SiGeオン・インシュレータ(SGOI)基板を製作する方法を提供することにある。

【解決手段】 この方法は、選択された平面内格子定数と、選択された厚さパラメータと、選択されたGe含有量パラメータとを有するSiGe合金層を有するSiGeオン・インシュレータ(SGOI)基板材料を提供するステップであって、選択された平面内格子定数が一定値を有し、他のパラメータ、すなわち、厚さまたはGe含有量の一方または両方が調整可能な値を有するステップと、選択された平面内格子定数を維持しながら、他のパラメータの一方または両方を最終選択値に調整するステップとを含む。この調整は、どのパラメータが固定され、どのパラメータが調整可能であるかに応じて、薄型化プロセスまたは熱希釈プロセスのいずれかを使用して達成される。

(もっと読む)

歪みシリコン・オン・インシュレータ(SSOI)およびこれを形成する方法

【課題】 コストが低く歩留まりの高い、引っ張り歪みSOI層を形成するための方法および引っ張り歪みSOI層の構造を提供する。

【解決手段】 歪みSiベースの層を製造するための方法、この層に製造されるデバイス、ならびに、かかる層およびデバイスを含む電子システムを開示する。この方法は、基板上にSiGe層をエピタキシャル成長させるステップと、このSiGe層において様々なGe濃度を生成するステップを含む。SiGe層内のGe濃度は、Ge濃度が突然かつ著しく増大する固有のGeオーバーシュート・ゾーンを含む。SiGe層上に、Siベースの層をエピタキシャル堆積させ、これによって引っ張り歪みが与えられる。また、典型的にSiまたはSiGeである歪みSiベースの層を、異なるバルク基板または絶縁体に転写可能であることも開示される。

(もっと読む)

21 - 35 / 35

[ Back to top ]