Fターム[5F152LN16]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | バッファ層、動作層 (308) | 多結晶,非晶質 (35)

Fターム[5F152LN16]の下位に属するFターム

低温成長 (19)

Fターム[5F152LN16]に分類される特許

1 - 16 / 16

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

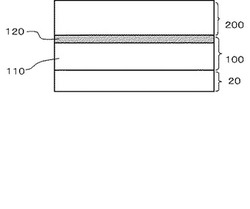

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

窒化物系III−V族化合物半導体装置の製造方法

【課題】バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供する。

【解決手段】SiC基板71上にAlNのバッファ層72を形成した後、AlNのバッファ層72上にGaN層を成長させる。続いて、AlNのバッファ層72と上記GaN層の界面近傍に、Gaイオンを打ち込んで、AlNのバッファ層72と上記GaN層の界面付近にアモルファスの層74を形成する。その後、基板温度を800℃まで上げてアモルファスの層74の上の上記GaN層を再結晶化して、転位が少ないGaN層75層を形成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

半導体基板の製造方法

【課題】III族窒化物半導体の結晶層の結晶性を向上できる半導体基板の製造方法を提供する。

【解決手段】本発明の第1側面に係る半導体基板の製造方法は、下地基板の上にクロム層を50℃以上の温度で成膜するクロム層成膜工程と、前記クロム層を窒化してクロム窒化物膜にする窒化工程とを備えたことを特徴とする。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】III族窒化物半導体の結晶層の結晶性を向上できる半導体基板の製造方法及び半導体基板を提供する。

【解決手段】本発明の第1側面に係る半導体基板の製造方法は、下地基板の上にクロム層を7nm以上45nm未満の平均層厚で成膜するクロム層成膜工程と、前記クロム層を1000℃以上の温度で窒化してクロム窒化物膜にする窒化工程とを備えたことを特徴とする。

(もっと読む)

半導体デバイスの製造方法

【課題】サファイア基板上に形成されるシリコンエピタキシャル層の品質向上を図ることにより、製造される半導体デバイスの特性を向上させること。

【解決手段】本発明は、SOS(シリコン・オン・サファイア)ウエハを用いた半導体デバイスの製造方法において、サファイア基板を準備する工程と;前記サファイア基板上にシリコン(Si)層を形成する工程と;前記シリコン層にシリコンイオンを注入する工程と;前記シリコンイオン注入の後に、前記シリコン層をエピタキシャル再成長させる工程とを含む。そして、前記シリコンイオン注入工程において、前記シリコン層の表面付近の結晶欠陥を有するシリコンの数を8E14未満とし;前記サファイア基板と前記シリコン層との界面付近における前記シリコンイオンの単位容積当たりの注入量を3.0E19 ions/cm3 以上とする。

(もっと読む)

AlN系III族窒化物結晶の作製方法およびAlN系III族窒化物厚膜

【課題】比較的簡便な手法によって低転位のAlN系III族窒化物厚膜を得ることができる方法を提供する。

【解決手段】所定の基材上にMOCVD法によってAlN系III族窒化物成長下地層が形成されてなるエピタキシャル基板の上に、HVPE法によってAlN系III族窒化物厚膜をエピタキシャル形成する場合に、MOCVD法における加熱温度よりも高い温度で該エピタキシャル基板を加熱処理した上で、厚膜層の形成を行うようにすることで、厚膜層の低転位化を実現することができる。すなわち、HVPE法を用いた厚膜成長に先立って、加熱処理という比較的簡便な処理を施すだけで、HVPE法による成長に際して特別の構成を有する装置を用いたり、あるいは成長条件に特段の限定を加えたりしなくとも、低転位のAlN系III族窒化物からなる厚膜層を形成することができる。

(もっと読む)

半導体積層体の形成方法

【課題】本願の目的は、Si基板上に結晶性と表面モフォロジーの良い単結晶SiC層を形成することにある。

【解決手段】本願の骨子は、Si層上にSiやSiCよりも融点の低いSiGe層と非晶質SiCを形成し、これら積層構造をSiGeの融点以上に加熱することにより、SiCとSi基板の間の歪みを緩和し、同時に非晶質SiCからの結晶化を行うことで、結晶性と表面諸フォジーが良好な単結晶SiC層を形成する。

(もっと読む)

SOSウェハおよびその製造方法

【課題】通常のシリコンウェハ加工装置において加工が可能なSOSウェハの反りを防止する手段を提供する。

【解決手段】サファイア基板の裏面に不透明なポリシリコン層を備えたSOSウェハにおいて、裏面側に、ポリシリコン層を保護する窒化シリコン層と、この窒化シリコン層の応力を打消す応力緩和膜を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SOI基板を用いることなく、絶縁体上に形成される半導体層の面積を拡大する。

【解決手段】 開口部7を介して空洞部9内の半導体基板1および第2半導体層3の熱酸化を行うことにより、半導体基板1と第2半導体層3との間の空洞部9に埋め込み絶縁膜10を形成した後、ソース/ドレイン層25a、25bの表面に露出している埋め込み絶縁膜10、13および第2半導体層3をパターニングすることにより、開口部7の周囲のソース/ドレイン層25a、25bの側壁を露出させるコンタクトホール26を形成し、コンタクトホール26を介してソース/ドレイン層25a、25bにそれぞれ接続された配線層27a、27bを形成する。

(もっと読む)

歪み層を成長させる方法

Si歪み層16をSi基板10上に形成する方法は、Si基板10上に第1のSiGeバッファ層12を形成するステップを含む。それから、イオン注入法を用いて、第1のSiGeバッファ層に非晶質化インプラントを注入し、第1のSiGeバッファ層を非晶質にする。アニール処理の前に、第1のSiGeバッファ層上に、第2のSiGeバッファ層14を成長させる。これにより、緩和SiGe層12,14を生成する。それから、Siの歪み層16を成長させる。  (もっと読む)

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

応力のかかるシステムのための基板および当該基板上での結晶成長法

本発明は、核生成層(2)、多結晶性または多孔性緩衝層(4)、および支持体基板(6)を含む結晶成長用支持体を提供する。 (もっと読む)

1 - 16 / 16

[ Back to top ]