Fターム[5F152LN14]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | バッファ層、動作層 (308) | 組成変化 (147) | 連続的に変化 (68)

Fターム[5F152LN14]に分類される特許

1 - 20 / 68

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

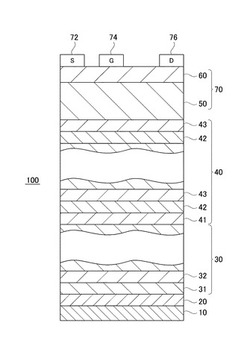

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

歪吸収中間層遷移モジュールを有するIII族窒化物半導体構造

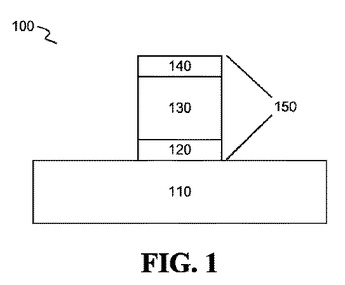

【課題】歪み吸収III族窒化物中間層モジュールを有する種々の半導体構造を提供する。

【解決手段】基板および当該基板の上方の第一遷移本体を有する。前記第一遷移本体は、第一表面において第一の格子パラメータを有し、前記第一表面とは反対側の第二表面において第二の格子パラメータを有する。前記典型的な実施では、遷移モジュール等の第二遷移本体をさらに有し、この第二遷移本体は前記第一遷移本体の前記第二表面に重層する下表面においてより小さい格子パラメータを有し、前記第二遷移本体の上表面においてより大きい格子パラメータを有し、前記第二遷移本体の上方のIII族窒化物半導体層も同様である。前記第二遷移本体は2以上の遷移モジュールからなっていてもよく、各遷移モジュールは2以上の中間層を有していてもよい。前記第一遷移本体および前記第二遷移本体は前記半導体構造の歪みを減少させる。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】デバイス活性層へのオートドーピングやミスフィット転位が発生し難く、且つ、デバイス形成後に薄厚化されても不純物金属によるデバイス活性層の汚染を有効に抑制することができるエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】シリコン基板の表面から内部に向かってV族原子を拡散させて形成した、濃度:2×1013atoms/cm3以上1×1018atoms/cm3以下のV族原子を含有してシリコン基板の表層に位置するバリア層と、バリア層上に形成したシリコンエピタキシャル膜よりなるデバイス活性層とを備えることを特徴とするエピタキシャルウェーハである。また、バリア層形成工程と、デバイス活性層形成工程とを含むエピタキシャルウェーハの製造方法である。

(もっと読む)

イオン・インプラント・アイソレーションによるLED製作

【課題】電気的に隔離された発光ダイオードを提供する。

【解決手段】半導体発光ダイオードは、半導体基板51と、基板上にあるn型III群窒化物のエピタキシャル層52と、n型エピタキシャル層上にあり当該n型層と共にp−n接合部を形成する、III群窒化物のp型エピタキシャル層53と、n型エピタキシャル層上にありp型エピタキシャル層に隣接し、p−n接合部58の一部を電気的に隔離する抵抗性窒化ガリウム領域54とを含む。p型エピタキシャル層上に金属接点層55を形成する。方法の実施形態では、p型エピタキシャル領域上に打ち込みマスクを形成し、p型エピタキシャル領域の部分にイオンを打ち込んでp型エピタキシャル領域の部分を半絶縁性にすることによって、抵抗性窒化ガリウム境界を形成する。フォトレジスト・マスク又は十分に厚い金属層を、打ち込みマスクとして用いることができる。

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

減少した転位パイルアップを有する半導体ヘテロ構造および関連した方法

【課題】緩和した格子不整合の半導体へテロ構造を提供すること。

【解決手段】組成的に勾配した半導体層における転位パイルアップは、減少もしくは実質的に除かれ、これによって、増加した半導体デバイス歩合および製造性に導く。このことは、組成的に勾配したバッファ層の後に続く成長および緩和の前のスタート層としておよび/または組成的に勾配した層の成長および緩和中の少なくとも1つの中間層としてその表面にわたり実質的に均一に分布する複数のスレッディング転位を有する半導体層を導入することによって達成される。この半導体層は、半導体層の表面に近接して位置するシード層、およびそこに均一的に分布するレッディング転位を有することを含み得る。

(もっと読む)

おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法

【課題】おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法。

【解決手段】本方法は、次の順序で工程:前記シリコン単結晶基板のおもて面及び裏面を同時に研磨する工程;応力補償層を前記シリコン単結晶基板の裏面上に堆積させる工程;前記シリコン単結晶基板のおもて面を研磨する工程;前記裏面上に堆積された応力補償層を有する前記シリコン単結晶基板を洗浄する工程;及びSiGeの完全に又は部分的に緩和された層を前記シリコン単結晶基板の前記おもて面上に堆積させる工程を含んでなる。

(もっと読む)

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

ウェーハおよびウェーハの製造方法

【課題】異なる格子の基板上に成長した良質なエピタキシャル層を備えたウェーハおよびウェーハ製造方法の提供。

【解決手段】単結晶の第1の材料の基板はオンアクシスシリコン基板であり、オンアクシスシリコン基板上に第2の材料を成長させるウェーハの製造方法に関し、第2の材料が、第1の材料上にエピタキシャル成長し、第1の材料の格子とは異なる格子を持っている。オンアクシスシリコン基板を研磨ステップ104で研磨して、ウェーハ表面粗さを増大させる。SiGe層である傾斜バッファ層及び緩和層をウェーハ上に形成した後、CMP最終研磨108を実施する。上述のタイプの方法により解決され、基板の最終表面仕上げの前に第2の材料の成長を実施する。

(もっと読む)

グレーデッドエピタキシャル成長を用いた半導体品の製造プロセス

【課題】緩和III−V族またはII−VI族マテリアルオンインシュレータの製造方法の提供。

【解決手段】緩和Si1−yGey層104を有する半導体構造の形成プロセスは、第1の基板上へのグレーデッドSi1−xGexバッファ層102の堆積であって、前記Ge濃度xはゼロから値yまで増加するものである堆積、緩和Si1−yGey層104の堆積、前記緩和Si1−yGey層104中にイオンを導入して第1のヘテロ構造を規定、前記第1のヘテロ構造を第2の基板108に接合して第2のヘテロ構造を規定、および前記導入されたイオンの領域での前記第2のヘテロ構造の分割であって、前記緩和Si1−yGey層104の表層部分は前記第2の基板上108に残るものである分割を含む。

(もっと読む)

シリコン上にバッファ層構造を形成する方法および当該方法により形成された構造

【解決手段】 微小電子デバイスを形成する方法および対応する構造を記載する。当該方法は、基板にGaSb核生成層を形成する段階と、GaSb核生成層にGa(Al)AsSbバッファ層を形成する段階と、Ga(Al)AsSbバッファ層にIn0.52Al0.48As下側バリア層を形成する段階と、In0.52Al0.48As下側バリア層にInxAl1−xAsグレーデッド層を形成する段階とを備えるとしてよい。当該方法によれば、欠陥の少ない、勾配をつけたInGaAsベースの量子井戸構造を有するデバイスを製造することができる。 (もっと読む)

エピタキシャル成長のための基板の作成方法

【課題】本発明は、補助基板上に緩和エピタキシャルベース層を得ることを含む、エピタキシャル成長のための基板の作製方法に関する。本発明の目的は、望ましい格子パラメータを有する材料が、異なる格子パラメータを有する別の材料の上で、より効率的に、熱力学的及び結晶学的に高い安定性を有してエピタキシャル成長することを可能にする基板を作ることにある。

【解決手段】この目的は、上記のタイプの方法であって、エピタキシャルベース層の少なくとも一部をキャリア基板上に移してベース基板を形成することと;エピタキシャルベース層の材料をキャリア基板上でさらに成長させることとをさらに含む方法により達成される。

(もっと読む)

半導体基板

【課題】従来に比べ極めて薄いバッファ層を用いて、工業的に安定でかつ低コストで、基板と格子定数の異なる良質の薄膜を形成した半導体基板を提供すること。

【解決手段】基板1は、格子定数xを有するものである。第1の半導体層2は、基板1上に形成され、格子定数yを有し、少なくともSbを含んでいる。第2の半導体層3は、第1の半導体層2上に形成され、格子定数yからzまで格子定数を段階的又は連続的に変化させものである。第3の半導体層4は、第2の半導体層3上に形成され、格子定数zを有するものある。これらの格子定数の関係は、x<z<yの関係を有している。基板1上に格子定数の異なる薄膜を形成する際に、まずSbを含む半導体を形成し、その上層に格子定数を変化させるためのバッファ層を形成することで、従来に比べ薄いバッファ層で結晶欠陥のない薄膜形成が可能となる。

(もっと読む)

画定された不純物勾配を有するひずみ材料層を使用する半導体構造、およびその構造を製作するための方法。

【課題】不純物の無い区域を有するひずみ材料層を含む半導体構造とデバイス、及びそれを製作するための方法を提供する。

【解決手段】ひずみ材料層104の特定の領域108は、半導体の隣接する部分から相互拡散することができる不純物を無い状態にしておく。不純物がひずみ材料層104の特定の領域108に存在する場合、デバイス性能の低下となる。説明された特徴を有する、又は説明されたステップに従って製作される半導体構造100とデバイス(例えば、電界効果トランジスタ、即ち「FET」)を使用することにより、デバイスの動作が向上する。

(もっと読む)

半導体基板の製造方法

【課題】

歪み層/歪み印加結晶層構造において、歪み印加結晶層構造より発生する結晶欠陥によ

る歪み層の結晶性劣化を低減し、かつ絶縁層上に歪み層/歪み印加結晶層構造を薄膜で形

成した基板の形成方法を提供する。

【解決手段】

Si基板上の絶縁層と、別の半導体基板上のSiGe層とを、半導体張り合わせ技術を

用いて接合し、SiGe層側の半導体基板を研磨等により除去する。

(もっと読む)

マイクロエレクトロニクス及びオプトエレクトロニクス向けSOI基板の製造方法

【課題】マイクロエレクトロニクス及びオプトエレクトロニクス向けSOI(SEMICONDUCTOR‐ON‐INSULATOR)基板の製造方法に関連し、単一基板上において、電子及びフォトニック部品のコインテグレーションを可能にする。

【解決手段】本発明の方法は、<110>又は<111>配向を有する薄いひずみシリコン層を支持する誘電材料から形成される1つの面を有する支持材を含む基板を供給する段階と、前記薄いひずみシリコン層の一部上に第一マスクを形成する段階と、Si1―XGeXのエピタキシー段階と、ゲルマニウム濃縮する段階と、前記第一マスク及び前記酸化シリコン層を除去する段階と、前記段階によって露出された前記薄い半導体層上に第二マスクを形成する段階と、残留ひずみゲルマニウムの部分上にゲルマニウムをエピタキシャル成長させる段階と、前記第二マスクを除去する段階とを含む。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

シリコン基板及びその製造方法

【課題】半導体素子を形成するためにエピタキシャル成長された半導体層による湾曲を抑制したシリコン基板を提供すること。

【解決手段】シリコン基板1において、窒化物系化合物半導体層2の成長によって凹状に反る方向に加わる圧縮応力と拮抗する応力が、シリコン基板1の窒素不純物濃度分布に対応した密度またはサイズの分布を有する酸素析出物の膨張力によって与えられたことを特徴とする、実質的に平坦な主面を有するシリコン基板、およびその製造方法。

(もっと読む)

中間層構造を有する窒化物半導体構造、及び中間層構造を有する窒化物半導体構造を製造する方法

半導体構造は、窒化物半導体材料の第1の層、前記窒化物半導体材料の第1の層上の実質的に歪みのない窒化物中間層、及び前記窒化物中間層上の窒化物半導体材料の第2の層を含む。前記窒化物中間層は第1の格子定数を有し、アルミニウム及びガリウムを含むこと、並びにn型ドーパントで導電的にドープすることができる。前記第1の層及び前記第2の層は、全体として少なくとも約0.5μmの厚さを有する。前記窒化物半導体材料は、前記第1の層が前記窒化物中間層の一方の側において、前記第2の層が前記窒化物中間層の他方の側で受け得るより大きい引っ張り歪みを受けることができるような、第2の格子定数を有することが可能である。  (もっと読む)

(もっと読む)

1 - 20 / 68

[ Back to top ]